Connect the printer usb to the lpt port of the computer. LPT port application

Ministry of Education and Science of the Russian Federation

Federal State Educational Institution

higher vocational education

"Komsomolsk-on-Amur State Technical University"

Department "Industrial Electronics"

Testing LPT-port of a personal computer

Guidelines for laboratory work on the course

"Debugging means of microprocessor systems" for students of the direction 210100 "Electronics and Nanoelectronics"

Komsomolsk-on-Amur 2013

Testing of the LPT-port of a personal computer: Guidelines for laboratory work on the course "Debugging Tools of Microprocessor Systems" for students of the 210100 "Electronics and Nanoelectronics" direction / Comp. CM. Hoofs - Komsomolsk-on-Amur: Komsomolsk-on-Amur State. tech. Univ., 2013. - 19 p.

The Centronics parallel interface, signals and software support for the LPT port of a personal computer are considered, and recommendations are given for testing it.

The proposed guidelines are intended for students directions 210100.

Reprinted by order of the editorial and publishing council of Komsomolsk-on-Amur State Technical University.

Agreed with the standardization department.

Reviewer V.A. Yegorov

Objective: learn the basic features of a standard LPT port. Understand the principles of software-controlled information exchange through a parallel port. Learn to check its performance.

1 basic information

1.1 Description of the parallel interface

Historically, a parallel interface was introduced into a personal computer (PC) to connect a printer (hence the abbreviation LPT - Line Printer - line printer). However, the parallel interface was later used to connect other peripheral devices (PUs). The basic version of the port allows data to be transferred only in one direction (from PC to PU), but later a number of standards for bi-directional data transmission were developed.

In modern office computers, an LPT port, as a rule, is not provided; however, by installing a multi-port expansion card, such a port can be placed at your disposal.

A parallel interface adapter is a set of registers located in the address space of input / output devices. The number of registers depends on the type of port, but three of them are standard and are always present. These are the data register, the status register and the control register. Register addresses are counted from the base, the standard values of which are 3BCh, 378h, 278h. A port can use a hardware interrupt (IRQ7 or IRQ9). Many modern systems allow you to change the port operation mode, its address and IRQ from the Base Input Output System (BIOS) Setup settings.

The LPT port has an external 8-bit data bus, a 5-bit status signal bus, and a 4-bit control signal bus. Obviously, the port is asymmetric 12 lines work for output and only 5 for input.

During the initial loading, the BIOS tries to detect the parallel port, and makes it a primitive and not always correct way. if the byte read coincided with the written one, it is considered that an LPT port was found at this address. The BIOS cannot detect the LPT4 port address. To work with the PU, the INT 17h interrupt is provided in the BIOS, which provides the ability to transfer data (byte-by-bye), initialize the PU and receive information about its state.

Centronics conceptrefers to the signal set, communication protocol, and 36-pin connector previously installed in printers. The purpose of the signals and the pins of the PU connector to which they are displayed are shown in Table 1.

Table 1 - Centronics Interface Signals

|

Direction |

Purpose |

|||

|

Data strobe. The computer is transmitted, the data is recorded at a low signal level. |

||||

|

Data lines D0 is the low bit. |

||||

|

Acknowledge - byte acknowledgment pulse (request to receive the next one). It can be used to form interrupts. |

||||

|

Busy Data reception is possible only when the signal level is low. |

||||

|

"1" signals the end of the paper |

||||

|

"1" signals that the printer is turned on (GP - receiver readiness), usually +5 V through a resistor from the power source PU) |

||||

|

Automatic line feed. If "0", then PU when receiving the symbol CR (carriage return) performs the function LF - line feed |

||||

|

Error PU (off-line, no paper, no toner, internal error) |

||||

|

Initialization (go to the beginning of the line, reset all parameters to default values) |

||||

|

Select a printer. With "1", the printer does not perceive the remaining interface signals. |

||||

|

Common wire |

Note: "T" column - active signal level: "1" - high active level, "0" - low active level. The column "Direction" - the direction of transmission in relation to the printer: I - Input (input), O - Output (output).

The Auto LF signal is practically not applied, but its incorrect value causes the printer to either skip lines, or print lines on top of each other, or duplicate lines when printing in two passes.

Domestic analogue of the Centronics interface is IRPR-M. In addition to it, there is an IRPR interface (outdated), which is distinguished by the exchange protocol, the absence of the “Error” signal and the inversion of data lines. In addition, a pair of terminating resistors are connected to all the input lines of the IGPR: 220 ohms to +5 V and 330 ohms to the common wire. This overloads most of the interface adapters of modern PCs.

The protocol of data exchange via the Centronics interface is shown in Figure 1.

Figure 1 - Centronics Interface Communication Protocol

Transmission begins with checking the source signal Error. If it is installed, the exchange is not made. It then checks the status of the Busy signal. If it is equal to "0", then the source proceeds to transfer the data byte. To transmit a byte, the source places data bytes on the D0-D7 line and outputs a Strobe # signal. The Strobe # signal receiver (hereinafter the "#" icon after the signal name is a sign that the signal is at a low active level) reads data from the data bus and sets the Busy signal at the time of its processing. At the end of processing, the receiver issues an ACK # signal and removes the Busy signal.

If the source does not receive an ACK # for a long time (6–12 sec.), It decides about the device’s time-out error. If, after receiving a byte, the receiver is not ready to receive data for any reason, then it does not remove the Busy signal. When software implements an exchange using the specified protocol, it is desirable to limit the waiting time for Busy withdrawal (usually 30 - 45 seconds), otherwise the program may hang.

The standard parallel port is called the SPP (Standard Parallel Port). The SPP port is unidirectional, on its base the Centronics exchange protocol is programmatically implemented. The port provides the ability to generate IRQ on an ACK # pulse at the input. The port signals are output to a standard DB-25S connector (socket), which is placed directly on the adapter board or connected to it with a flat cable (in case the adapter is integrated with the motherboard).

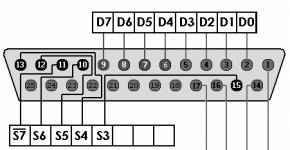

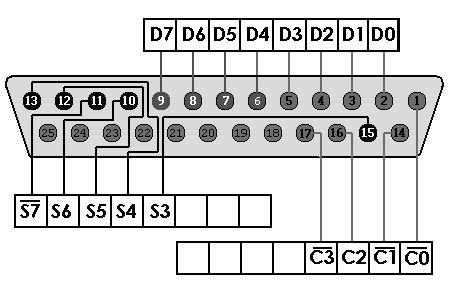

The names of the signals correspond to the names of the signals of the Centronics interface (Table 1), and the image of the interface adapter connector from the computer is shown in Figure 2.

Table 2 - Connector and loop of standard LPT port

|

Wire loop | |||||||

|

10, 22, 14, 16, 18, 20, 22, 24, 26 |

Note. I / O - transmission direction: I - input; O is the output; O (I) is the output, the state of which can be read under certain conditions, O / I - output lines, the state of which is read when reading from the corresponding port registers. * - ACK # input is connected to +5 V power through a 10 kΩ resistor. This is done to eliminate false interrupts, because An interrupt is generated by a negative signal drop at the ACK # input.

Figure 2 - Cetronics DB-25S Interface Adapter Connector

As disadvantages of the standard LPT port (SPP), it is necessary to note the low data transfer rate (100-150 kB / s), processor load during data transfer, the impossibility of bidirectional byte exchange. There is a “radio amateur” method of bidirectional exchange, which consists in setting “1” for data input on the D0-D7 line, and using an open collector chip as a transmitter, which, when the transistor is open, can “pull” the voltage of the logical unit to the level order 1.5 - 1.7 V. The current is limited to 30 mA. As is evident from the signal levels, they do not correspond to TTL levels, so many ports do not work in this mode or are unstable. In addition, this method can be dangerous for the port adapter, which will work with current limits for it.

IEEE 1284 standard, adopted in 1994, defines the terms SPP, EPP, and ECP. The standard defines 5 data exchange modes, mode matching method, physical and electrical interfaces. According to IEEE 1284, the following modes of data exchange through a parallel port are possible:

Compatibility Mode - unidirectional (output) using the Centronics protocol. This mode corresponds to the standard SPP port;

Nibble Mode - input bytes in two cycles (4 bits each), using to enter the status line. This exchange mode can be used on any adapters;

Byte Mode - enter the entire byte using data lines for receiving. This mode works only on ports that can read output data (Bi-Directional or PS / 2 Type 1);

EPP (Enhanced Parallel Port) Mode - bidirectional data exchange, in which interface control signals are generated by hardware during a port access cycle (read or write to the port). Effective when working with external memory devices, LAN adapters;

ECP (Extended Capability Port) Mode - bidirectional exchange with the possibility of hardware data compression by the method of RLE (Run Length Encoding), the use of FIFO-buffers and DMA. Interface control signals are hardware generated. Effective for printers and scanners.

In modern machines with an LPT port on the motherboard, the port mode is SPP, EPP, ECP, or a combination of them is set in BIOS Setup. Compatibility Mode is fully SPP compliant and is often set by default. All other modes extend the functionality of the interface and increase its performance. In addition, the standard regulates the way in which the mode available on both the PC and the peripheral device is coordinated.

Physical and electrical interface.The IEEE 1284 standard defines the physical characteristics of receivers and signal transmitters. It is significant that the transmission uses TTL logic levels.

The IEEE 1284 standard defines three types of connectors used: A (DB-25S), B (Centronics-36), C (the new 36-pin compact connector). Interface cables can have from 18 to 25 conductors (depending on the number of GND conductors). Conventional cables can only work at low speeds with a length of no more than 2 meters. Improved shielded cables with signal wires intertwined with common wires can be up to 10 meters long. Such cables are labeled as "IEEE Std 1284 - 1994 Compliant".

Work with parallel port at low level (i.e., at the level of direct access to the port controller) it is used for solving a variety of tasks related to the exchange of information with non-standard devices, for writing printer drivers and a number of other tasks. Direct work with the controller allows you to implement any communication protocol with the device and use the port lines at your discretion.

The port controller is located in the address space of I / O devices and is accessed via the IN and OUT commands of the assembler. Information about the LPT1 - LPT3 ports can be obtained by reading the BIOS variables shown in Table 3.

Table 3 - BIOS Variables for LPT Ports

|

Port name |

BIOS address |

Variable type |

Description |

|

The base port address is LPT1. If the variable is 0, then the LPT1 port is not found. |

|||

|

Timeout constant |

|||

|

The base port address is LPT2. If the variable is 0, then the LPT2 port is not found. |

|||

|

Timeout constant |

|||

|

The base port address is LPT3. If the variable is 0, then the LPT3 port is not found. |

|||

|

Timeout constant |

|||

|

The base port address is LPT4. If the variable is 0, then the LPT4 port is not found. |

|||

|

Timeout constant |

The BIOS searches for ports at Base: 3BCh, 378h, 278h. LPT4 BIOS port can not find:

378h - parallel adapter LPT1;

278h - parallel adapter LPT2;

3BCh - LPT3 parallel adapter.

The standard port has three 8-bit registers located at adjacent addresses, starting with the base (Base) address. The list of registers is given in table 4.

Table 4 - Registers of standard LPT port

Data Register (DR).The data recorded in this register is output to the output lines of the D0D7 interface. The result of reading this register depends on the adapter circuitry and corresponds either to the previously recorded data or to the signals on the D0D7 lines, which is not always the same. With standard inclusion, the first option is valid - the read data is equal to the previously recorded.

Status Register (SR). It is a 5-bit input port, which receives status signals from an external device. Allows only reading. The assignment of the bits of this register is given in table 5.

Table 5 - SR Status Register Bits

|

Title |

Purpose |

|

|

Inverse display of the state of the Busy line (11). At low level on line 11 (Busy) - the bit is equal to "1" - PU is ready to receive the next byte |

||

|

Displays the status of the ACK # line (10). "0" - acknowledgment, "1" - normal condition |

||

|

Displays the status of the Paper End line (12). "0" is the norm, "1" - there is no paper in the PU |

||

|

Displays the status of the Select line (13). "0" - PU is not selected, "1" - PU is selected |

||

|

(inverse) |

Display the status of the line Error (15). "0" is a PU error, "1" is a normal state |

|

|

ACK # interrupt flag (PS / 2 only). Reset if ACK # triggers a hardware interrupt. "1" - after reset or after reading the status register |

||

|

Not used (reserve) |

Control Register (CR).The control register is a 4-bit output port that can be read and written. Bits 0, 1, 3 are inverted, i.e. "1" in these bits of the control register corresponds to "0" on the corresponding lines of the port. The assignment of the control register bits is given in Table 6. Bit 5 is used only for bidirectional ports.

Table 6 - CR Register Control Bits

|

Title |

Purpose |

|

|

Port direction control bit. "1" - input mode, "0" - output mode |

||

|

ACK # interrupt generation control bit. "1" - enable ACK decay interrupt # (10) |

||

|

SLCT IN # line control (17). "1" - the printer is enabled. |

||

|

Line Management INIT # (16). "1" is the normal state, "0" is a hardware reset of the PU |

||

|

Auto LF # line control (14). "1" - enable the "Auto LF" mode, "0" - the normal state |

||

|

Strobe # line control (1). "1" - data gating, "0" - normal state |

Interface programming. To develop application programs, you must select a programming language. If you need a simple, fast and compact program that does not contain complex computational operations, then to write it is better to choose a low-level language (assembly language). Assembly language refers to a group of machine-oriented languages, i.e. each microprocessor family has its own language.

A high-level language should be chosen if it is necessary to perform complex calculations, or if a high program performance is not required. Object codes obtained as a result of broadcasting programs written in a high-level language usually take up much more space in the computer's memory and are executed slower compared to programs in assembly language. Often, an approach is used where the speed-critical parts of a program are written in assembler, and computational procedures in a high-level language, for example, in Pascal or C.

Consider working with the registers of the CENTRONICS interface in PASCAL or assembler:

X is a number of type "byte" (0..255). For example, when sending 170 10 = = 10101010 2 on the d0 – d7 line, a single signal will be present on the d1, d3, d5, d7 terminals (the pin designation starts with d0). The number 170 will remain on the pins of the connector until you send another number there (another program can do this) or turn off the computer. Note that the port address in the command is given in hexadecimal, and the package is in decimal. If instead of Pascal team

Port [$ 378]: = 170;

You apply

where d is a variable, the variable will take the value of the last byte sent to the port or, when switching to receive mode, the value of the byte sent to the port by an external device.

An example of reading the Pascal status register:

In the variable d, after the program is executed, the status of the port will be displayed. Suppose the variable returns the value 126 10. In binary form, it looks like 01111110 2. The low (right) three bits (zero, first and second) are not used, and are almost equal to 1, 1 and 0. The third bit is 1, which means a high level on ERROR. The same situation on SELECT, Paper End, ACK and BUSY (do not forget that the BUSY signal is inverted).

Here is an example of a fragment of a program that reads bytes from data lines D0-D7:

Port [$ 37A]: = 32; 32 "includes" unit in the fifth

d: = Port [$ 378]; bit, putting the port in input mode

As can be seen from the above examples, programming an LPT port is a very simple task, which makes it possible to greatly facilitate the work of a device software developer with the interface under discussion.

1.2 Testing LPT-port

Testing of LPT-port can be performed using a simple plug, which can be made using table 7.

Table 7 - Table chains stub for testing LPT-port

|

Direction |

Direction | ||||

The “LPT” port is rarely found on modern computers. This is a special computer connector for connecting a printer. Some computers were equipped with several LPT ports. These ports were numbered: "LPT1", "LPT2" and so on.

Parallel ports

Historically, the ports for connecting a computer are divided into categories: serial and parallel ports. "LPT" refers to parallel ports. This means that information travels along eight different wires, that is, simultaneously and in parallel. Computers deal with binary information. Binary transforms information into arrays of zeros and ones. One binary number (zero or one) is called a bit. A group of eight bits is called a byte. The eight bits of each byte that are moved from the computer to the parallel port are moved simultaneously. Another type of cable connected to the serial port moves eight bits of each byte one by one.

Value

The parallel port has a name. The default name for the single parallel port of the computer is “LPT1”. This type of port is mainly used to connect the printer. Other devices can be connected to these ports, however, users use the printer much more often than other devices. Connecting the printer to the computer makes it "peripherals". "Peripheral" can be any device connected with a special cable to a computer. This "peripheral" equipment can only be used by one computer at a time. The only way to connect an already connected “peripheral” device to another computer is to use a printer connected to the first computer — using the network and software. This process is different from a network printer that connects to a network, and not to one computer. In this case, a different type of cable and a different type of port are used.

Connection

The parallel port "LPT" and the corresponding connector has 25 pins and is called "DB-25" or "D-Type 25". In the connector pins are bare. They fit into the 25 holes of the parallel port. Eight of the 25 pins are responsible for transferring data, the rest are either control data or printer instructions like messages from the printer about the absence of paper in the printer.

Future

Network printers are connected to the computer not through the “LPT” port, but through the “Ethernet” port. Not only a printer, but also other devices can be connected to the LPT port. Today, "peripheral" devices do not use parallel ports. Both “LPT” ports and serial ports today are history and replaced by a “USB” port or a network port. The ability to wirelessly connect new printers and peripherals provides another alternative to the “LPT” port as a way to connect the printer to a computer.

The computer processes signals in parallel streams, so it is easier for it to “communicate” with parallel, rather than with serial external ports. In 1984, as part of the IBM PC, a parallel port first appeared. It was conceived as a means of connecting matrix printers, hence the name LPT - Line PrinTer or Line Printer Terminal. Later, printers began to use high-speed USB interface, and the LPT-port began to be gradually replaced by computer specifications. The crooks compare LPT with a suitcase without a handle - and it’s pathetic to throw it away, and it’s impossible to haul it. Nevertheless, the "veteran" is still capable of much, if, of course, he is present in a particular computer.

The LPT port has 25 pins. The “de facto” norm is considered to be a DB-25F socket in a computer and a DB-25M plug in a return cable (Table 4.2). The numbering of the contacts of the plugs and sockets is mirror (Fig. 4.7, a, b).

Table 4.2. The layout of signals in the 25-pin connector LPT-port

|

Decryption |

Direction |

Enter exit |

Enter exit |

the confirmation |

Readiness |

No paper |

Autotransfer |

Enter exit |

Initialization |

Enter exit |

Input selection |

Enter exit |

Fig. 4.7. External appearance of the 25-pin LPT-port connectors: a) a DB-25F socket in the computer; b) DB-25M plug in the connecting cable.

Initially, the LPT port lines were unidirectional SPP (Standard Parallel Port). Some of them worked only at the input, part - only at the output, which corresponded to the Centronics printer interface in terms of the signal set and exchange protocol. In 1994, a new IEEE 1284 parallel interface standard was approved, providing for bi-directional lines and three modes of operation: SPP, EPP (Enhanced Parallel Port), ECP (Extended Capabilities Port).

Levels of electrical signals LPT-port coincide with the usual "five-volt" logic chips. Previously, computers used buffer TTJl-chips of the 74LSxx series, later - CMOS chips and LSI, roughly equivalent to the 74ACxx series. In the latter case, we can tentatively assume that the LOW level is 0.1..0.2 V, and the HIGH - 4.5 ... 4.9 V.

The standard regulates the load of 14 mA for each output while maintaining a voltage of at least +2.4 V HIGH and no more than +0.4 V LOW. However, in different motherboards, the output buffers of the LPT port may have different load capacity, including lower than the standard (“weak” port).

Requirements for connecting cables connected to the LPT port:

Signal wires must be twisted in pairs with a common wire GND;

Each pair must have an impedance of 56 ... 68 Ω in the frequency range 4 ... 16 M Hz;

If a flat ribbon cable is used, the signal wires must physically alternate with a common GND wire (local shields);

The level of crosstalk between signals is not more than 10%;

The cable must have a shield covering at least 85% of the outer surface. At the ends of the cable, the shield should be ringed and connected to the “earth” connector terminal;

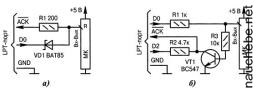

In the cable connector, you can solder to the contacts 1 ... 17 series resistors C2-23 (OMJIT-O.125) with a resistance of 100 ... 300 Ohms (Fig. 4.8). This will protect the computer from accidental short circuits in the load and reduce high-frequency "ringing" on the fronts of signals.

![]()

Fig. 4.8. Electric circuit of LPT cable with “anti-ring” resistors.

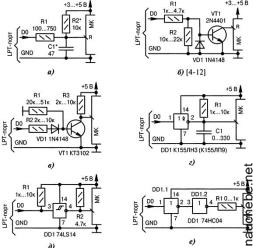

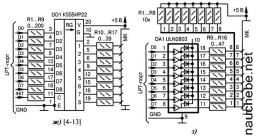

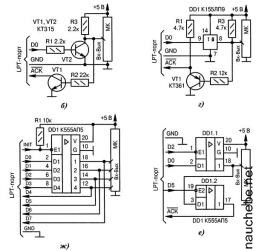

MK connection circuits with LPT port can be divided into three groups:

Reception of signals from a computer (Fig. 4.9, and ... h);

Transmission of signals to a computer (Fig. 4.10, a ... e);

Reception / transmission of signals simultaneously (Fig. 4.11, a ... e).

The schemes adopted some simplifications. The input signal is indicated mainly “DO”, and the output signal is “ACK”, although there may be others listed in Table. 4.2. On each specific computer, the performance of self-made circuits must be checked experimentally, which is due to the presence of “strong” and “weak” LPT ports according to their load capacity.

Fig. 4.9. Signal input schemes from LPT-port to MK (start):

a) resistor R1 limits the input current. Elements R2, C1 may be absent, but they reduce the "ringing" on the fronts of signals with a long cable;

b) the buffer transistor VT1 inverts the signal. Diode VD1 is not necessary, but it protects the transistor from the erroneous supply of a large negative voltage. If the R2 resistor is not installed, the circuit will remain operable, however, if the cable is disconnected from the LPT port, the VT1 transistor can be falsely affected by external noise and interference;

c) the diode VD1 cuts off interference and raises the threshold of operation of transistor VT1. Resistor R1 reliably closes the transistor VT1 at a LOW level from the LPT port;

d) buffer logic element DD1 has an open collector output. The signal fronts are formed by the elements R1, C1. Instead of the inverter DD1, you can install a K155LP9 repeater by making the appropriate changes in the MK program and the computer;

d) Schmitt trigger DD1 (replacement - K555TL2) increases noise immunity. The lower the resistance of resistors R1, R2, the greater the steepness of the signal fronts. When the cable from the LPT port is disconnected, the R1 resistor does not allow the DD1 input to “hang in the air”;

e) the sequential inclusion of two logical elements DD11, /)/)/.2 increases (restores) the steepness of the signal fronts. Resistor R1 eliminates the emission, "ringing";

Fig. 4.9. Signal input schemes from LPT-port to MK (end):

g) the data coming from the LPT port is previously placed in the intermediate register DD1. The recording is made at the HIGH level at the input "C" of the chip DD1, storage - at LOW. Such a solution eliminates interference, since random data may be periodically output to the LPT port, depending on the drivers installed in the computer. They are eliminated programmatically, for example, by repeatedly reading the input signal from the MK lines;

h) the buffering of the LPT port with powerful transistor keys located in a DA Instrument chip by Texas Instruments. Resistors R1 ... R8 can have 10 ... 15 times lower resistance, which allows you to connect in parallel the outputs of the chip A4 / other nodes of the device.

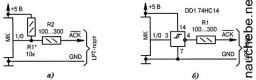

Fig. 4.10. Signal output from MK to LPT-port (start):

a) direct connection of the MK output without buffer elements. Resistors R1, R2 reduce the reflection of signals in the line. In addition, resistor R2 protects the MK output from an accidental short circuit with a GND circuit in the wires of the connecting cable;

b) Schmitt trigger DD1 serves as a protective buffer for MK in case of an emergency at the output (short circuit or high voltage supply);

c) DD1 microcircuit has an open collector output, which protects it from a short circuit in the wires and connectors of the connecting cable;

d) supply of two antiphase signals to the computer. The goal is a program need or organization of a duplicate (control) data transmission channel;

d) optical isolation on the elements HL1, BL1, which are used in computerized mechanical "mice". Transistor KG / amplifies and inverts the signal. For normal operation of the device, the computer must set the HIGH level on the “D8” line.

Fig. 4.11. Combined signal input / output schemes between MK and LPT port (start):

a) if the computer sets the “DO” line to HIGH, the MK in the output mode can generate the “ACK” signal through the resistor R1. If MK is switched to the input mode, the computer can transmit data through the “DO” line through the VD1 diode while the internal “pull-up” MK resistor generates a HIGH level;

b) the signal from the LPT port is inputted into the MK via the inverter on the transistor VT1 and the computer must set the HIGH level on the “D2” line. Information is entered into the MK from the “DO” line through the resistor R1. The high resistance of the resistor R1 physically decouples the input and output channels;

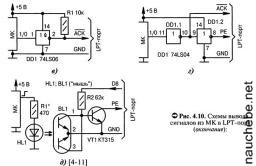

Fig. 4.11. Combined signal input / output circuits between MK and LPT port (ending):

b) the signal from the LPT port is inputted to the MK via an inverter on the transistor VT1, while the computer must set the LOW level on the “DO” line. Information in the MC is entered through the elements R1, R3, VT2;

d) the signal from the LPT port is entered into the MK via a repeater on the transistor VT1, and the computer must set the HIGH level on the “DO” line. Information is entered into the MK through a repeater on the chip DD1 \\

g) “D0” ... “D3” signals are entered into the MK at a LOW level on the “INIT” line, while the computer must configure the “D4” ... “D7” lines as inputs. In the BIOS settings of the computer, you must set the bidirectional EPP or ECP mode for the LPT port. Information is transmitted to the computer from the MC via the “D4” ... “D7” lines at the HIGH level on the “INIT” line. Resistor R1 translates the outputs of DD1 chip to the Z-state when the cable is disconnected from the LPT port;

e) the signal from the MK is entered into the LPT port through a DD1.2 repeater, while the computer must set the HIGH level on the “D2” line and the LOW level on the “D5” line. Information in the MK is entered through the repeater DD1.1 at a LOW level on line "D2". Gating signals to the inputs "E1", "E2" chip DD1 increases the reliability of data transmission.

Parallel port and RPR

Most modern peripherals connected to LPT-nop-tu support the 1284 standard and PnR functions. To support these functions by computer from a hardware point of view, it is enough to have an interface controller conforming to the 1284 standard. If the connected device supports RPR, it can negotiate with the port representing the "interests" of the computer about possible exchange modes using the 1284 mode negotiation protocol. Further, for the operation of the RPR, the connected device must provide the operating system with all the necessary information about itself. At a minimum, these are manufacturer identifiers, models and a set of supported commands. More detailed device information may contain a class identifier, a detailed description and a device identifier with which compatibility is ensured. In accordance with accepted information to support this device, the operating system may take steps to install the required software.

Devices with RRP support are recognized by the OS at the stage of its loading, if, of course, they are connected to the port with an interface cable and their power is turned on. If Windows detects a connected PnR device that is different from what is written in its registry for this port (or just a new device), it tries to install the required drivers for the device from the OS distribution kit or from the distribution kit of the new device. If Windows does not want to notice the newly connected PnR device, this may indicate a malfunctioning port or cable. The PnR system does not work if the device is connected with a cheap “non-bidirectional” cable that does not have a connection via the Selectln # line (pin 17 of the LPT port and pin 36 of the Centronics connector).

Typically, LPT-port is used to connect the printer (see. P. 8.3.1), but this does not exhaust its application.

To connect two computersover a parallel interface, different cables are used depending on the modes of the ports used. The simplest and slowest is the nibble mode working on of allports. For this mode, the cable is enough to have 10 signal and one common wire. Wiring cable connectors are given in Table. 1.11. The connection of two PCs with this cable is supported by standard software such as Interlnk from MS-DOS or Norton Commander.

High-speed communication between two computers can also be performed in the ESR mode (the EPP mode is inconvenient, since it requires synchronization of bus I / O cycles of two computers).

Connection scannerto LPT port is effective only if the port provides at least two-way mode (Bi-Di),since the main thread is input. It is better to use the ESR port if this mode is supported by the scanner (or EPP, which is unlikely).

Connection external drives(Iomega Zip Drive, CD-ROM, etc.), lAN adaptersand other balanced I / O devices have their own specifics. In the SPP mode, along with the slowing down of the device operation, the principal asymmetry of this mode is noticeable: reading datahappens two times slower than(very slow) recordApplication bidirectionalregime (Bi-Dior PS / 2 Ture 1)eliminate this asymmetry - speeds are equal.Only by going to EPP or ECP can one get normalspeed of work. In the EPP or ESR mode, the connection to the LPT port is almost as fast as the connection through the ISA controller. This is also true when connecting devices with a standard bus interface to LPT ports via interface converters (for example, LPT - IDE, LPT - SCSI, LPT - PCMCIA). Note that the IDE hard drive, connected via an adapter to the LPT port, can be represented as a SCSI device for the system (this is more logical from a software point of view).

2. Serial interfaces

The serial interface for data transmission uses one signal line, through which information bits are transmitted one after the other sequentially. Hence the name of the interface and port. English terms - Serial interface and Serial part (sometimes they are incorrectly translated as "serial"). Sequential transmission reduces the number of signal lines and increases the communication range. A characteristic feature is the use of non-TTL signals. In a number of serial interfaces, galvanic isolation of external (usually input) signals from the circuit earth of the device is used, which allows to connect devices that are under different potentials. The interfaces RS-232C, RS-422A, RS-423A, RS-485, current loop, MIDI, as well as the COM port will be discussed below.

2.1. Serial Transfer Methods

Serial data transmission can be carried out in asynchronous or synchronous modes. With asynchronous transmission to each byte is preceded by start bit, signaling to the receiver about the beginning of the package, followed by data bits and, perhaps, parity bit (parity) Completing the parcel stop bit, guaranteeing a pause between shipments (Fig. 2.1). The start bit of the next byte is sent at any time after the stop bit, that is, there can be pauses of arbitrary duration between transmissions. A start bit, which is always strictly defined (logical 0), provides a simple mechanism to synchronize the receiver with a signal from the transmitter. It is understood that the receiver and transmitter operate at the same rate of exchange. The internal synchronization generator of the receiver uses a counter-divider of the reference frequency, reset at the moment of receiving the start of the start bit. This counter generates internal gates, in which the receiver records the following received

bits Ideally, the gates are located in the middle of the bit intervals, which allows you to receive data even with a slight discrepancy between the receiver and transmitter speeds. Obviously, when transmitting 8 data bits, one control and one stop bit, the maximum permissible velocity mismatch at which the data will be recognized correctly cannot exceed 5%. Taking into account the phase distortions and the discreteness of the internal synchronization counter operation, a smaller frequency deviation is actually permissible. The smaller the dividing ratio of the reference frequency of the internal oscillator (the higher the transmission frequency), the greater the error in strobe binding to the middle of the bit interval, and the requirements for frequency coherence become more stringent. The higher the transmission frequency, the greater the influence of the distortion of the edges on the phase of the received signal. The interaction of these factors leads to increased requirements for the consistency of the receiver and transmitter frequencies with increasing exchange frequency.

Asynchronous sending format allows you to identify possible transmission errors:

» If a differential signaling the beginning of the package is received, and the level of the logical unit is fixed at the start-bit gate, the start-bit is considered false and the receiver again goes into the standby state. The receiver may not report this error.

“If during the time allotted for the stop bit, a logic zero level is detected, a stop bit error is detected.

"« If parity is applied, then after sending the data bits are transmitted check bit This bit complements the number of single data bits to even or odd, depending on the convention adopted. Accepting a byte with the wrong control bit value results in an error being committed.

The format control allows detecting a line break:

in this case, a logical zero is accepted, which is initially treated as a start bit, and zero data bits, then the stop bit control is triggered.

For asynchronous mode adopted a number standard exchange rates: 50, 75, 110, 150,300,600,1200,2400,4800,9600, 19,200, 38,400, 57,600 and 115,200 bps. Sometimes baud (baud) is used instead of the “bps” unit, but this is incorrect when considering binary transmitted signals. In bauds, it is customary to measure the frequency of line state changes, and with a non-binary coding method (widely used in modern modems), the bit rate (bit / s) and signal changes (baud) in the communication channel may differ several times (see Appendix A for details ).

amount data bit may be 5, 6, 7 or 8 (5- and 6-bit formats are not widely distributed). Number of stop bit may be 1, 1.5 or 2 (“one and a half bits” means only the duration of the stop interval).

Asynchronous exchange in the PC is implemented using COM port with using protocol RS-232C.

Synchronous The transfer mode assumes that the communication channel is always active. The package starts with a sync byte, immediately followed by a stream of information bits. If the transmitter has no data to transmit, it fills in a pause by continuously sending synchronization bytes. Obviously, when transferring large data arrays, the synchronization overhead in this mode will be lower than in asynchronous. However, in synchronous mode, external synchronization of the receiver with the transmitter is necessary, since even a small frequency deviation will lead to a distortion of the received data. External synchronization is possible either by using a separate line for transmitting the synchronization signal, or by using self-synchronizing data coding, in which at the receiver side synchronization pulses can be extracted from the received signal. In any case, synchronous mode requires expensive communication lines or terminal equipment. For PC, there are special cards - SDLC adapters (expensive) that support synchronous exchange mode. They are used mainly for communication with large machines (mainframes) IBM and are not widely used. Of the synchronous adapters, V.35 interface adapters are currently used.

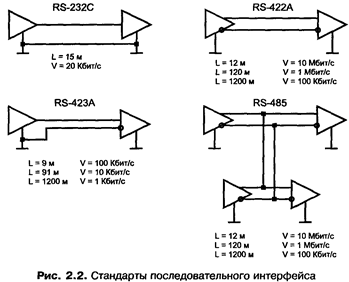

On physical level The serial interface has various implementations that differ in the way electrical signals are transmitted. There are a number of related international standards: RS-232C, RS-423A, RS-422A and RS-485. In fig. 2.2 shows the connection schemes of receivers and transmitters, and also shows the restrictions on the length of the line (L) and the maximum data transfer rate (V).

Unbalanced lines of interfaces RS-232C and RS-423Ahave the lowest common mode immunity, although the differential input of the receiver RS-423A somewhat softens the situation. The best options has a point-to-point interface. RS-422A and its trunk (tire) analogue RS-485 working on symmetric communication lines. They use differential signals with a separate (twisted) pair of wires to transmit each signal.

In the listed standards the signal is represented potential. There are serial interfaces where the current flowing through a common transmitter / receiver circuit - “current loop” and MIDI is informative. For communication over short distances, wireless infrared standards have been adopted. The most common PC received the simplest of these - the standard RS-232C,implemented by COM ports. In industrial automation is widely used RS-485 and RS-422A, occurring in some printers. There are signal converters for matching these related interfaces.

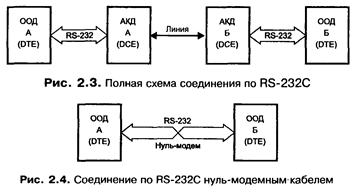

2.2. RS-232C interface

The interface is designed to connect the equipment transmitting or receiving data. (OOD - data terminal equipment or ADF - data transmission equipment; DTE - Data Terminal Equipment), to terminal equipment data channels (DCE; DCE - Data Communication Equipment). The ADF can be a computer, printer, plotter, and other peripheral equipment. In the role of the DCE is usually a modem. The ultimate goal of the connection is to connect two ADF devices. The full wiring diagram is shown in fig. 2.3. The interface allows you to exclude a remote communication channel along with a pair of ADF devices by connecting the devices directly using a null modem cable (Fig. 2.4).

The standard describes interface control signals, data transfer, electrical interface, and connector types. The standard provides asynchronous and synchronous exchange modes, but COM ports only support asynchronous mode. Functionally RS-232C is equivalent to the CCITT V.24 / V.28 standard and the C2 junction, but they have different signal names.

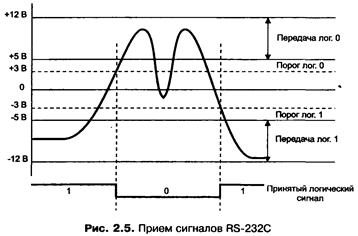

2.2.1. Electrical interface

Standard RS-232C uses unbalanced transmitters and receivers — the signal is transmitted relative to the common wire — circuit ground (symmetrical differential signals are used in other interfaces — for example, RS-422). Interface DOES NOT PROVIDE GALVANIC BREAKDOWN devices. The logical unit corresponds to the voltage on receiver input in the range of -12 ...- 3 V. For control signal lines, this state is called ON ("Enabled"), for serial data lines - MARK. The logical zero corresponds to the range +3 ... + 12 V. For control signal lines, the state is called OFF ("Off"), and for serial data lines - SPACE. The -3 ... + 3 V range is the dead zone causing the receiver hysteresis: the state of the line will be considered changed only after the threshold is crossed (Fig. 2.5). The signal levels at the transmitter outputs should be in the -12 ...- 5 V and +5 ... + 12 V ranges to represent the unit and zero, respectively. The potential difference between the circuit lands (SG) of the connected devices must be less than 2 V, with a higher potential difference, the signals may not be correctly perceived. The interface assumes the presence of PROTECTIVE GROUNDING for connected devices, if both of them are powered by AC power and have network filters.

Connecting and disconnecting interface cables self-powered devices must be made with power off. Otherwise, the difference between the unaligned potentials of the devices at the time of switching may be applied to the output or input (which is more dangerous) interface circuits and damage the microcircuit.

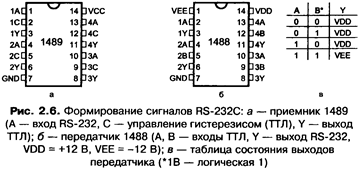

For interface RS-232C Buffer chips of receivers are specially produced (with hysteresis and bipolar signal transmitter). If grounding and switching rules are not followed, they are usually the first victims of “pyrotechnic” effects. Sometimes they are installed in "beds", which facilitates the replacement. Pinout of signal conditioner chips RS-232C is shown in fig. 2.6. Often, buffer schemes are included directly in the interface LSI. This reduces the cost of the product, saves space on the board, but in case of an accident, it results in large financial losses. Disabling interface chips by closing signal circuits is unlikely: the transmitter short-circuit current usually does not exceed 20 mA.

Standard RS-232C regulates types of connectors used.

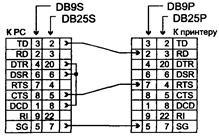

On hardware ADF (including on COM ports) it is customary to install forks (male - "dad") DB-25P or more compact option - DB-9P. Nine-pin connectors do not have pins for additional signals required for synchronous operation (most pins do not use these pins for most 25-pin connectors).

On hardware AKD (modems) install sockets(female - "mother") DB-25Swm DB-9S.

This rule assumes that the connectors AKD can connect to connectors ADF directly or through transitional "direct" cables with a socket and plug, in which the contacts are connected "one to one". Adapter cables can also be adapters from 9- to 25-pin connectors (Fig. 2.7).

If the equipment ADF connects without modems, the device connectors (plugs) are interconnected null modem cable (Zero-modem or Z-modem), having on both ends of the outlet, the contacts of which are connected crosswise according to one of the schemes shown in Fig. 2.8.

If on any device ADF a socket is installed - this is almost a 100% sign that it must be connected to another device with a straight cable, similar to a modem connection cable. The socket is usually installed on those devices that do not have a remote connection via modem.

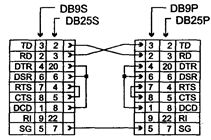

In tab. 2.1 shows the pin assignment of the COM port connectors (and any other equipment). ADF). The pins of the DB-25S connector are defined by the EIA / TIA-232-E standard, the DB-9S connector is described by the EIA / TIA-574 standard. For modems, the name of the circuits and contacts is the same, but the roles of the signals (input-output) are reversed.

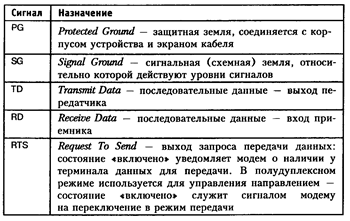

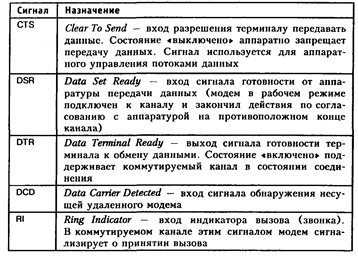

Subset of signals RS-232C, related to the asynchronous mode, consider from the point of view of the COM port of the PC. It should be remembered that the active state of the signal ("on") and logical unit transmitted data corresponds to negative potential (below -3 V) of the interface signal, and the “off” state and logical zero - positive (above +3 V). The purpose of the interface signals is given in Table. 2.2.

1 * - 8-bit multicard loop.

2 * - 16-bit multicard cable and ports on the motherboards. 3 * - a variant of a loop of ports on motherboards. 4 * - wide cable to the 25-pin connector.

2.2.2. Flow control

To control the flow of data (Flow Control) can be used two versions of the protocol - hardware and software. Sometimes flow control is confused with handshaking, but these are different methods of achieving the same goal — coordinating the rate of transmission and reception. Acknowledgment(Handshaking) involves sending a notification of receipt of an item, while flow control involves sending a notification about the impossibility of subsequent data reception.

Hardware flow control protocol RTS / CTS (Hardware Flow Control) uses the CTS signal, which allows you to stop data transmission if the receiver is not ready to receive them (Fig. 2.9). The transmitter "releases" the next byte only when the CTS line is on. A byte that has already begun to be transmitted cannot be delayed by a CTS signal (this guarantees the integrity of the message). The hardware protocol provides the fastest response of the transmitter to the state of the receiver. Chips asynchronous transceivers have at least two registers in the receiving part -

shifting, for receiving the next parcel, and storing, from which the received byte is read. This allows the exchange of hardware protocol without data loss.

The hardware protocol is convenient to use when connecting printers and plotters, if they support it (Fig. 2.10). With direct (without modems) connecting two computers, the hardware protocol requires cross-connecting RTS - CTS lines.

If the hardware protocol is not used, the transmitting terminal must be enabled on the CTS line with an RTS-CTS jumper. Otherwise, the transmitter will be “silent”.

XON / XOFF flow control software protocol assumes a bi-directional data channel. The protocol works as follows: if the device receiving the data detects the reasons for which it can no longer receive them, it sends a byte-character on the reverse serial channel Xoff (13h) The opposite device, by adopting this symbol, suspends transmission. When the receiving device is again ready to receive data, it sends the symbol

XON (llh), accepting that the opposite device resumes transmission. The response time of the transmitter to a change in the state of the receiver, as compared with the hardware protocol, is increased at least by the time the symbol is transmitted (XON or XOFF) plus the response time of the transmitter program to the reception of a symbol (Fig. 2.11). From this it follows that lossless data can only be received by a receiver that has an additional buffer of received data and signals unavailability in advance (with free space in the buffer).

The advantage of the software protocol is that there is no need to transfer interface control signals - the minimum cable for two-way exchange can have only 3 wires (see Fig. 2.8a). The disadvantage is, apart from the requirement of having a buffer and a longer response time (reducing the overall performance of the channel due to waiting for the signal XON) is the difficulty of implementing a full duplex exchange mode. In this case, the flow control characters should be extracted (and processed) from the stream of received data, which limits the set of transmitted symbols. Minimum cable option for connecting a printer (plotter) with a protocol XON / XOFF is shown in fig. 2.12.

In addition to these two common standard protocols supported by both PU and OS, there are others. Some serial plotters use software control but do not send standard characters. XON / XOFF, but the words (ASCII strings). Such an exchange at the level of system protocol support is practically not supported (these plotters directly “talk” with the application program). Of course, you can write a COM port driver (interceptor INT 14h), but the need to process text messages from an output device in it usually doesn’t excite a system programmer. The connection cable is the same as shown in fig. 2.12.

2.3. Interface "current loop"

A common variant of the serial interface is the current loop. In it, the electrical signal is not the voltage level relative to the common wire, but current in a two-wire line connecting the receiver and transmitter. A logical unit (“on” state) corresponds to a current flow of 20 mA, and a logical zero - no current. Such a representation of the signals for the described asynchronous sending format allows detecting a line break - the receiver will notice the absence of a stop bit (line break acts as a permanent logical zero).

The current loop usually involves galvanic isolation receiver input circuits from the device circuit. In this case, the source of current in the loop is the transmitter (this variant is called the active transmitter). It is also possible to receive power from the receiver (active receiver), while the transmitter's output key can also be electrically isolated from the rest of the transmitter circuitry. There are simplified variants without electrical isolation, but this is a degenerate case of the interface. The current loop with galvanic decoupling allows you to transmit signals over distances up to several kilometers. The distance is determined by the resistance of the pair of wires and the level of interference. Since the interface requires a pair of wires for each signal, usually only two interface signals are used. In the case of bidirectional exchange, only signals of the transmitted and received data are used, and the program method is used to control the flow. XON / XOFF. If bidirectional exchange is not required, a single data line is used, and to control flow, the return line is activated for the CTS (hardware protocol) signal or the opposing data line (software protocol).

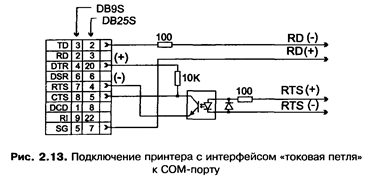

Convert signals RS-232C in the current loop, you can use an uncomplicated scheme (Fig. 2.13). Here the printer is connected via a current loop to the COM port with hardware flow control. To obtain a bipolar signal required for the input signals of the COM port, power is applied from the interface.

With proper software of one current loop, bidirectional half-duplex communication of two devices can be provided. In addition, each receiver "hears" both the transmitter signals on the opposite side of the channel and the signals of its transmitter. They are considered communication packets simply as an echo. For accurate reception, the transmitters must operate alternately.

2.4. MIDI interface

Digital interface of musical instruments MIDI(Musical Instrument Digital Interface) is a bidirectional serial asynchronous interface with a transmission frequency of 31.25 Kbps. This interface, developed in 1983, became the de facto standard for interfacing computers, synthesizers, recording and reproducing devices, mixers, special effects devices, and other electromusical equipment.

The interface applies such a loop 10 mA (5 mA possible) with galvanic isolation of the input circuit. This eliminates the connection of the “schematic lands” of the connected devices via an interface cable, eliminating interference, which is extremely undesirable for sound equipment. The choice of the transmission frequency, which coincides with one of the quantization frequency values received in the digital sound recording, also serves to reduce interference interference.

Asynchronous package contains start bit, 8 bits of information and 1 stop bit, parity is absent. The high bit of the parcel is a “command / data” flag. Its zero value indicates the presence of seven bits of data in the lower bits. With a single value, the bits contain command code and bits - channel number. Commands can be either addressed to a specific channel or broadcast addressless. The last group includes start, stop and timestamp commands that provide device synchronization (synchronization system MIDI Sync and MTS - MIDI Time Code).

The interface defines three types of ports: MIDI In, MIDI Out nMIDI-Thru.

MIDI In port represents the input interface of the “current loop 10 mA”, galvanically isolated from the receiver by an optocoupler with a speed not worse than 2 μs. The device monitors the information flow at this input and responds to commands and data addressed to it.

MIDI Out port represents the output of the current source 10 mA, galvanically connected to the device circuit. The limiting resistors protect the output circuits from damage caused by a short to earth or a 5 V source. Information flow from this device is output to the output. The stream can also contain a translated input stream.

MIDI Thru Transit Port (optional) is used to relay the input signal.

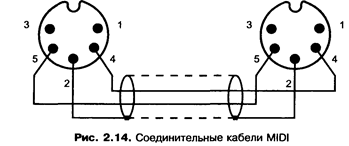

5-pin DIN connectors used in household audio equipment are used as connectors. Sockets are installed on all devices, plugs on cables. All MIDI connecting cables are unified (Fig. 2.14). Pin 2 - cable shield - connects to the common wire only on the transmitter side (connectors MIDI Out and MIDI Thru).

In the marking of the inputs and outputs, indicated near the connectors, there are discrepancies. Some manufacturers write "In" or "Out" in accordance with the connector function of this device (and this) is correct), then any cable connects "In" and "Out". Others believe that the signature should indicate the function of the device being connected. Then the cable will connect the connectors with the symbols "In" - "In" and "Out" - "Out".

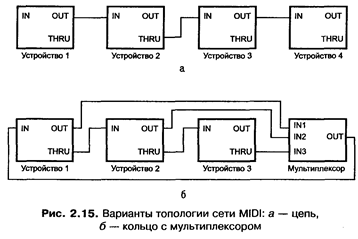

The interface allows you to combine a group of up to 16 devices in a local network. Topology must obey the rule:

entrance MIDI In single device must be connected to the output MIDI Out or MIDI Thru other. When planning a MIDI network, you must be guided by information flows and communication devices. Control devices — keyboards, sequencers (in playback mode), timing sources — must be in front of the controlled ones. If devices need a bi-directional exchange, they are connected in a ring. You can use special multiplexers that allow you to logically switch multiple input streams into one output. A degenerate ring case is the bidirectional connection of two devices. Several connection options are shown in Fig. 2.15.

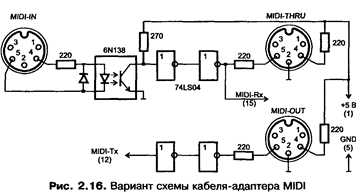

The PC has a MIDI port on most audio adapters, its signals are output to unused pins (12 and 15) of the game adapter connector. MIDI devices required for connecting adapter adapter realizing interface "current loop". The adapter is usually embedded in a special cable, the circuit of which is shown in fig. 2.16. Some PC models have built-in adapters and standard 5-pin MIDI connectors.

PC-compatible MIDI ports are used for the controller. MPU-401 (Roland) in UART mode. In the I / O space MPU-401 occupies two adjacent addresses MPU (usually 330h) and MPU + 1:

"» Port Data (address MPU + 0) - Record and read bytes sent and received via MIDI. Port STATUS / COMMAND (address MPU + 1) - status reading / command writing (write - for intellectual mode only). The following bits are defined in the status byte:

Bit 7 - DSR (Data Set Ready) - Ready (DSR-0) received data to read. The bit is set to “I” when all received bytes are read from the data register.

Bit 6 - DRR (Data Read Ready) - Ready (DRR = 0)UART to write to the data or command register. A readiness condition will not occur if the receiver has an unread data byte.

Some motherboards use LSI interface controllers, in which the UART used for the COM port can be set to MIDI mode by configuring via the BIOS SETUP.