AVR šeimos „Atmel“ mikrovaldikliai. „Atmel“ etiketė: „Atmel“ nestabilios atminties mikroschemos su nuoseklia sąsaja

Federalinė geležinkelių transporto agentūra

Tolimųjų Rytų valstybinis geležinkelių transporto universitetas

Telekomunikacijų katedra

Kurso projektas

Disciplina: „Mikroprocesorių informacijos valdymo sistemos“

Tema: „Atmel AVR šeimos mikrovaldikliai“

chabarovskas

Įvadas

Klasikinėje mikroprocesoriaus sistemoje naudojamas atskiras procesoriaus lustas, atskiri atminties lustai ir atskiri įvesties / išvesties prievadai. Spartiam mikroprocesorių technologijos tobulėjimui reikia vis daugiau ir daugiau didesnis laipsnis lusto integracija.

Štai kodėl buvo sukurtos mikroschemos, kurios iškart sujungia visus mikroprocesorinės sistemos elementus. Tokie mikroprocesoriai vadinami mikrovaldikliais. Sovietmečiu tokie mikroschemos buvo vadinamos „vieno lusto mikrokompiuteriais“.

Vieno lusto mikrovaldikliams sąvoka „centrinis procesorius“ paprastai nenaudojama. Kadangi procesorius vis dar yra atskiras įrenginys. Procesoriaus funkcijas mikrovaldiklyje keičia aritmetinis loginis blokas (ALU).

Be ALU, mikrovaldiklyje yra:

♦ laikrodžių generatorius;

♦ duomenų atmintis;

♦ programos atmintis;

♦ I / O jungtys.

Visi šie elementai yra sujungti vidiniais duomenimis ir adresų magistralėmis. Mikrovaldiklis susisiekia su išoriniu pasauliu naudodamas I / O prievadus. Bet kuris mikrovaldiklis visada turi vieną ar kelis prievadus. Be to, šiuolaikiniai mikrovaldikliai visada turi įmontuotą pertraukimo sistemą, taip pat įmontuotus programuojamus laikmačius, komparatorius, skaitmeninio-analoginio keitiklius ir daug daugiau.

Jei mes kalbame ne apie didelį kompiuterį, o apie nešiojamąjį valdymo įrenginį, tada jis naudojasi mikrovaldikliais. Žinoma, bet kuri reali grandinė retai būna be paprastų loginių schemų, gaidukų, skaitiklių ir pan. Bet pagrindas visada yra mikrovaldiklis. Gryni mikroprocesoriai šiuo metu naudojami tik asmeniniuose kompiuteriuose.

1. „Atmel“ mikrovaldiklis ATtiny2313 / V

1.1 Struktūra, pagrindinės savybės ir galimybės

„ATtiny 2313“ mikroschema yra aštuonių bitų mikrovaldiklis, turintis 2 kt vidinę programuojamą „Flash“ atmintį.

♦ naudoja AVRRISC architektūrą;

♦ AVR yra greita ir ypatinga RISC architektūra, sunaudojanti mažai energijos;

♦ 120 galingų instrukcijų, kurių dauguma vykdoma per vieną mašinos ciklą;

♦ 32 aštuonių bitų bendrosios paskirties registrai;

♦ visiškai statiška organizacija (mažiausias dažnis gali būti lygus 0);

♦ iki 20 milijonų operacijų per sekundę (MIPS / sec), esant 20 MHz takto dažniui.

Programų ir duomenų taupymas išjungus maitinimą:

♦ 2 kbaitai integruotos programuojamos „Flash“ atminties, iki 10000 įrašymo / ištrynimo ciklų;

♦ 128 baitai vidinės programuojamos nestabilios duomenų atminties (EEPROM);

♦ iki 10 000 įrašymo / ištrynimo ciklų;

♦ 128 baitai vidinės RAM (SRAM);

♦ programuojami programos atminties ir EEPROM skaitymo ir rašymo apsaugos bitai.

Išoriniai įrenginiai:

♦ vienas 8 bitų laikmatis / skaitiklis su programuojamu determinantu ir atitikties režimu;

♦ vienas 16 bitų laikmatis / skaitiklis su programuojamu determinantu, atitikties ir fiksavimo režimais;

♦ keturi kanalai PWM (PWM);

♦ įmontuotas analoginis lygintuvas;

♦ programuojamas budėjimo laikmatis ir įmontuotas laikrodžių generatorius;

♦ universali serijinė sąsaja USI (Universal Serial Interface);

♦ Visiškas dvipusis USART.

Mikrovaldiklio savybės:

♦ specialus derinimo WIRE įėjimas integruotai derinimo sistemai valdyti;

♦ intrasistemos programuojama serijinė sąsaja SPI;

♦ išorinių ir vidinių trikdžių šaltinių palaikymas;

♦ trys mažo vartojimo režimai (laukimo režimas, išjungimas ir budėjimo režimas);

♦ įmontuota aparatūros atstatymo sistema įjungus maitinimą;

♦ vidinis derinamas laikrodis;

♦ įvesties-išvesties grandinės ir korpusas;

♦ 18 programuojamų I / O linijų;

♦ trijų rūšių atvejai;

PDIP– 20 kontaktų;

SOIC - 20 kaiščių;

QFN / MLF - 20 kaladėlių.

Maitinimo įtampa:

♦ 1,8 - 5,5 V (ATtiny2313V);

♦ 2,7–5,5 V („ATtiny2313“).

„ATtiny2313V“ laikrodžio dažnių diapazonas:

♦ 0–4 MHz, esant 1,8–5,5 V įtampai;

♦ 0-10 MHz, esant 2,7–5,5 V įtampai.

ATtiny2313 laikrodžio dažnių diapazonas:

♦ 0-10 MHz esant 2,7–5,5 V įtampai;

♦ 0–20 MHz esant 4,5–5,5 V įtampai.

Aktyviosios srovės sunaudojimas:

♦ 1 MHz, 1,8 V: 230 μA;

♦ 32 kHz, 1,8 V: 20 μA (su vidiniu generatoriumi).

Dabartinis suvartojimas mažo vartojimo režime:

♦ ne daugiau kaip 0,1 μA esant 1,8 V įtampai.

Mikrovaldiklio bloko schema

„ATtiny2313“ mikroschemos kaiščių priskyrimas parodytas fig. 1. Mikrovaldiklio ATtiny2313 blokinė schema parodyta fig. 2.

AVR šerdyje yra didelis instrukcijų rinkinys darbui su 32 bendrosios paskirties registrais. Visi 32 registrai yra tiesiogiai sujungti aritmetiniu logikos bloku (ALU), kuris leidžia vykdyti dviejų skirtingų registrų komandą viename sistemos generatoriaus laikrodyje. Tokia architektūra leido pasiekti dešimt kartų didesnį našumą nei tradicinių mikrovaldiklių, pastatytų naudojant CISC technologiją.

Fig. 1 - „ATtiny2313“ lusto kaiščių priskyrimai

1.2 „ATtiny2313“ lusto savybės

„ATtiny2313“ lustas turi šias savybes:

♦ 2 kbitai programuojamų „Flash“ atminties programų;

♦ 128 baitai EEPROM;

♦ 128 baitai SRAM (RAM);

♦ 18 eilučių įvesties ir išvesties (I / O);

♦ 32 darbo registrai;

♦ vieno laido sąsaja, skirta suderinti grandinėje;

♦ du daugiafunkciai laikmačiai / skaitikliai su suderinimo funkcija;

♦ išorinių ir vidinių trikdžių palaikymas;

♦ nuoseklus programuojamas USART prievadas;

Fig. 2 - mikrovaldiklio ATtiny2313 blokinė schema

♦ universali nuosekli sąsaja su paleidimo perdavimo detektoriumi;

♦ programuojamas budėjimo laikmatis su vidiniu generatoriumi;

♦ Trys programuojami energijos taupymo režimai.

Laukimo režime centrinis procesorius yra sustabdytas, likusios sistemos toliau veikia. Išeiti iš šio režimo įmanoma tiek dėl išorinių trikdžių, tiek dėl vidinių. Pvz., Kai laikmatis perpildomas.

„PowerDown“ režimu registrų turinys išsaugomas, tačiau vidinio generatoriaus veikimas sustabdomas, o visos kitos lusto funkcijos yra išjungtos. Išeiti iš režimo galima dėl išorinio pertraukimo arba atstačius sistemą. Šis sprendimas leidžia suderinti greitą paleidimą su mažomis energijos sąnaudomis.

Lustas pagamintas naudojant unikalią „Atmel“ aukšto dažnio technologiją. Vidinę programų „Flash“ atmintį galima perprogramuoti naudojant IPT sąsają, nepašalinant mikrovaldiklio nuo plokštės. 8 bitų RISC procesoriaus ir sistemoje perprogramuojamos „Flash“ atminties derinimas viename luste daro „ATtiny2313“ lustą galingu įrankiu, kuris teikia labai lanksčius ir nebrangius sprendimus daugeliui valdymo programų.

Mano kursiniame projekte bus aprašyta tam tikra mikrovaldiklio dalis.

2. Centrinis procesoriaus branduolys

Pagrindinė centrinio procesoriaus branduolio funkcija yra valdyti programos vykdymo procesą. Norėdami tai padaryti, centrinis procesorius turi turėti tiesioginę prieigą prie atminties, sugebėti atlikti visų rūšių skaičiavimus ir vykdyti pertraukimo užklausas.

Apsvarstykite bendruosius AVR architektūros klausimus.

2.1 Trumpas architektūros aprašymas

Norėdami kiek įmanoma pagreitinti darbą ir suteikti galimybę atlikti kelias operacijas lygiagrečiai, AVR mikrovaldikliai naudoja „Howard“ architektūrą (3 pav.).

Fig. 3 - AVR architektūros blokinė schema

Tokia architektūra suteikia atskirą atmintį ir atskirą adresų magistralę tiek programai, tiek duomenims.

Kiekviena penkių programų komanda vykdoma viename mašinų cikle, naudojant daugiapakopį vamzdynų apdorojimą. Tuo metu, kai vykdoma kita komanda, kita programa skaitoma iš programos atminties. Ši koncepcija leidžia vykdyti vieną komandą per kiekvieną sistemos generatoriaus laikrodžio ciklą. Programinės įrangos atminties segmentas yra fiziškai integruota perprogramuojama „Flash“ atmintis.

Greitosios prieigos registrų rinkmenoje yra 32 aštuonių bitų bendrosios paskirties registrai, kurie pasiekiami per vieną sistemos generatoriaus laikrodžio ciklą. Tai leidžia aritmetiniam loginiam blokui (OLU) atlikti didžiąją dalį operacijų per vieną laikrodžio ciklą.

Įprasta ALU operacija atliekama taip: iš registro failo nuskaitomi du operandai ir atliekama operacija. Įrašymo rezultatas vėl įrašomas į registro failą. Visi trys šie veiksmai atliekami per vieną laikrodžio ciklą.

Šeši iš šių 32 registratorių gali būti naudojami kaip trys 16 bitų netiesioginiai adresų rodyklių registrai. Šie dvigubi registrai gali būti naudojami duomenims adresuoti RAM adresų erdvėje. Tokia organizacija leidžia programiškai apskaičiuoti adresą.

Vienas iš šių rodyklių registrų taip pat gali būti naudojamas kaip duomenų, esančių programos atmintyje („Flash“ atmintyje), rodyklė. Šie papildomi sudėtiniai 16 bitų registrai yra vadinami X, Y ir Z.

ALU palaiko aritmetines ir logines operacijas tarp dviejų registratorių arba tarp konstanto ir registratoriaus. ALU taip pat gali atlikti operacijas su atskirais registratoriais. Po kiekvienos aritmetinės operacijos būsenos registras atnaujinamas, kad atspindėtų informaciją apie jo rezultatą.

Programos vykdymo seka gali būti pakeista sąlyginėmis ir besąlygiškomis šakų komandomis, taip pat paprogramės iškvietimo komanda, kuri naudoja tiesioginį adresų skyrimą.

Dauguma AVR nurodymų yra vienas 16 bitų žodis. Kiekviename programos atminties adrese yra 16 bitų arba pusė 32 bitų instrukcijos.

Kai vykdoma pertraukimo rutina ar paprogramė, dabartinė komandų skaitiklio (PC) vertė saugoma krūvoje.

Rinkinys iš tikrųjų yra toje pačioje adresų erdvėje su SRAM duomenų atmintimi (RAM), todėl krūvos dydį riboja tik SRAM dydis ir tai, kokią SRAM dalį naudoja likusi programos dalis.

Vartotojo programa būtinai turi inicijuoti rodyklės rodyklę (SP) iškart po atkūrimo (prieš vykdant paprogramę arba iškviečiant pertraukimą). Rietuvos rodyklė (SP) turi savo konkretų adresą įvesties / išvesties registro vietoje. RAM duomenis galima pasiekti naudojant atmintį skirtingais būdais adresus palaiko AVR architektūra.

Visų rūšių atminties adresų sritis AVR architektūroje yra taisyklinga linijinė. Lanksčiame pertraukimo modulyje yra keletas valdymo registratorių, esančių I / O registrų adresų erdvėje, ir papildoma vėliava visuotinei pertraukimo raiškai būsenos registre.

Kiekvienas pertraukimo tipas pertraukimų vektorių lentelėje turi savo atskirą vektorių. Pertraukimai turi pirmenybę atsižvelgiant į jų vietą pertraukimų vektorių lentelėje. Kuo mažesnis pertraukimo vektoriaus adresas, tuo didesnis prioritetas.

I / O registracijos erdvėje yra 64 periferinių įrenginių valdymo registrų, procesoriaus režimo valdymo registrų ir kitų I / O funkcijų adresai. Bet kurį įvesties / išvesties registrą galima pasiekti tiesiogiai jo numeriu arba kaip duomenų atminties elementą. Duomenų atminties adresų srityje I / O registrai yra iškart po bendrosios paskirties registro failo (0x20 - 0x5F).

2.2 ALU - aritmetinis loginis įtaisas

Labai efektyvus ALU veikia tiesiogiai palaikant ryšį su visais 32 bendrosios paskirties registrais. Vienam laikrodžio generatoriaus ciklui aritmetinė operacija atliekama tarp dviejų RON arba tarp RON ir tiesiogiai nurodytos konstantos. Visos ALU operacijos yra suskirstytos į tris pagrindines kategorijas:

♦ aritmetika;

♦ logiška;

♦ operacijos su išmetimais.

Architektūros bruožas yra tas, kad atliekant aritmetines operacijas, visi operandai gali būti laikomi ir nepasirašytais, ir pasirašytais skaičiais.

Būsenos registras

Būsenos registre yra informacijos apie paskutinės aritmetinės ar loginės komandos rezultatus. Ši informacija gali būti naudojama programos vykdymo procesui pakeisti sąlyginės šakos instrukcijose ir kituose sąlyginiuose teiginiuose.

Kai iškviečiamas pertraukimo apdorojimo procesas, būsenos registras nėra automatiškai išsaugomas. Programuotojas į pertraukiamųjų duomenų apdorojimo procedūrą būtinai įtraukia komandas, kurios pradžioje įrašys šio registro turinį, o pabaigoje jį atkurs. Atminkite, kad būsenos registras negali būti tiesiogiai perkeltas į kamino atmintį. Pirmiausia turite išsaugoti vieną iš bendrųjų registrų krūve, tada įregistruoti būsenos registro turinį į išlaisvintą registrą, o tada perkelti informaciją iš tarpinio registro į krūvą.

Bendrojo registro byla

Registro failas yra optimizuotas AVRRISC instrukcijų rinkiniui. Norint pasiekti reikiamą našumą ir lankstumą, registro failas palaiko šias I / O schemas:

♦ vieno 8 bitų operando išvestis ir vieno 8 bitų skaičiavimo rezultato įvedimas;

♦ dviejų 8 bitų operandų išvestis ir vieno 8 bitų skaičiavimo rezultato įvedimas;

♦ dviejų 8 bitų operandų išvestis ir vieno 16 bitų skaičiavimo rezultato įvedimas;

♦ vieno 16 bitų operando išvestis ir vieno 16 bitų skaičiavimo rezultato įvedimas.

Fig. 4 parodyta 32 bendrosios paskirties registrų, naudojamų kaip mikrovaldiklio darbo registrai, struktūra.

Fig. 4 - AVR mikrovaldiklio bendrosios paskirties registrų byla

Daugelis nurodymų, veikiančių su registrų failais, turi tiesioginę prieigą prie visų jo registrų, o dauguma jų vykdomi per vieną laikrodžio ciklą.

Kaip parodyta fig. 5, kiekvienas registras taip pat atitinka adresą duomenų atminties vietoje, kur jie užima pirmąsias 32 ląsteles. Nors fiziškai registrai nėra SRAM dalis, ši atminties tvarka suteikia daugiau lankstumo prieinant prie registrų. Netiesioginę atminties prieigos rodyklę (vieną iš registrų X, Y arba Z) galima nustatyti bet kuriame registre iš failo.

2.3. X registras, Y registras ir Z registras

Registrai R26-R31, be pagrindinio tikslo, turi ir papildomą funkciją. Šie registrai gali būti naudojami kaip 16 bitų adreso rodyklės operacijoms naudojant netiesioginį adresų skyrimą. Trys netiesioginiai adresų registrai X, Y ir Z yra apibrėžti taip, kaip parodyta fig. 5.

Įvairiose komandose, naudojančiose netiesioginį adresų teikimą, šie registrai gali būti naudojami kaip pastovaus adreso šaltiniai, kaip adresų registras su automatiniu adreso didinimu ir kaip registras su automatiniu adreso mažinimu.

Fig. 5 - dvigubi registrai X, Y, Z

Stack žymeklis

Daugiausia naudojama krūva:

♦ laikinam duomenų saugojimui;

♦ saugoti vietinius kintamuosius;

♦ išsaugoti paprogramės išėjimo adresą arba nutraukti rutiną.

Rietuvės rodyklės registras visada rodo į jo viršų.

Rietuvės rodyklė nurodo rietuvės sritį duomenų atmintyje (SRAM). Ant kamino, be kita ko, jie yra išsaugomi;

♦ paprogramės išėjimo adresas;

♦ išėjimo iš pertraukimo tvarkymo tvarkos adresas.

Todėl bet kurioje programoje krūvos pradžios adresas turi būti nustatytas prieš iškviečiant paprogramę ir prieš pašalinant pertraukimus. Iš pradžių rietuvės rodyklę reikia nustatyti ne mažesniu kaip 0x60 adresu.

Rietuvės rodyklė sumažėja viena, kai duomenys įrašomi į krūvą naudojant komandą PUSH, ir sumažėja dviem, kai krūva užrašoma grąžinimo adresu iš paprogramės arba nutraukiama tvarkymo rutina.

Rietuvės rodyklė padidinama vienetu, kai duomenys nuskaitomi iš krūvos naudojant POP komandą, ir padidinama dviem, kai duomenys ištraukiami iš krūvos, kai išeinama iš paprogramės (RET komanda) arba baigiamas pertraukimo apdorojimo rutinas (RETI komanda).

Visų AVR lustų rietuvės rodyklė yra padaryta dviejų 8 bitų I / O registrų pavidalu. Kiekvieno mikrovaldiklio modelio iš tikrųjų išleidžiamų teršalų skaičius yra skirtingas. Kai kuriuose modeliuose, įskaitant ATtiny2313, duomenų atminties kiekis yra toks mažas, kad rietuvės rodyklė naudojama tik mažiausia iš rietuvės rodyklės registrų (SPL). Nėra SPH registro. Mikrovaldiklio ATtiny2313 rietuvių rodyklių struktūra parodyta žemiau.

Atmintis ATtiny2313

Dabar apsvarstykite įvairių rūšių mikrovaldiklio atmintis ATtiny2313. AVR architektūroje yra du pagrindiniai atminties tipai:

♦ duomenų atmintis;

♦ programos atmintis.

Be to, „ATtiny2313“ lustas turi EEPROM atmintį ilgalaikiam duomenų saugojimui. Visi trys atminties tipai yra ištisiniai regionai, kurių adresai tiesiškai didėja.

2.4 Sistemos blykstės programuojama blykstės programa

„ATtiny2313“ luste yra 2 KB vidinės perprogramuojamos atminties programų saugojimui. Kadangi visos AVR naudojamos komandos yra 16 arba 32 bitų dydžio, programos atmintis organizuojama kaip 1Rx 16. Grafine forma programos atminties adreso sritis parodyta fig. 6.

Fig. 6 - programos atminties kortelė

Programos atmintis leidžia bent 10 000 įrašymo / ištrynimo ciklų. „ATtiny2313“ lusto komandų skaitiklis (PC) turi 10 bitų, todėl gali veikti su 1K adreso erdve. Mikroschema palaiko nedidelį programos atminties programavimo režimą, kurį galima įgyvendinti per nuosekliąją SPI sąsają.

Programos atmintyje taip pat galite patalpinti duomenis, kurie programos veikimo metu nepakito. Norėdami gauti šiuos duomenis iš programos atminties, naudokite komandą LPM.

2.5 SRAM duomenų atmintis

Fig. 6 parodyta ATtiny 2313 mikrovaldiklio duomenų atminties - RAM (SRAM) - organizacija. Iš viso RAM adresų erdvėje yra 224 langeliai, kurie yra užimti:

♦ bendrojo registro byla;

♦ papildomi įvesties-išvesties registrai;

♦ vidinė duomenų atmintis.

Pirmieji 32 langeliai yra suderinti su RON failu. Kiti 64 langeliai yra standartinė sritis, kurioje yra visi įvesties ir išvesties registrai. Ir tik likę 128 langeliai sudaro vidinę duomenų atmintį.

Yra penki skirtingais būdais adresai duomenų atminčiai:

♦ tiesioginis;

♦ netiesiogiai su šališkumu;

♦ netiesioginis;

♦ netiesiogiai su patikslinimu;

♦ netiesioginis su padidinimu.

Registrai R26-R31 (X, Y, Z) naudojami kaip adreso indikatoriai visoms operacijoms, kurių adresai yra netiesioginiai.

Tiesioginiam adresavimui nurodomas visas duomenų baito adresas.

Netiesiogiai kreipiantis su ofsetu, įmanoma aplenkti 63 langelius, pradedant nuo dabartinio bazinio adreso, kurį nurodo Y arba Z registro turinys.

Kai naudojamas netiesioginis adresavimas su automatiniu išankstiniu mažinimu ir automatiniu mažinimu po perskaitymo (rašymo) atminties, pasikeičia X, Y arba Z registre įrašytas adresas.

Visoje adresų metodų atmintyje yra visi 32 bendrosios paskirties registrai, 64 I / O registrai ir 128 baitai „ATtiny2313“ lusto SRt duomenų atminties.

EEPROM duomenų atmintis

ATtiny2313 luste yra 128 baitai EEPROM atminties. Ji yra suorganizuota kaip atskira duomenų saugojimo adresų erdvė, kurioje kiekvienas baitas gali būti atskirai skaitomas arba rašomas.

Duomenų mainai tarp EEPROM ir centrinio procesoriaus yra aprašyti žemiau ir vyksta naudojant:

♦ EEPROM adreso registravimas;

♦ EEPROM duomenų registras;

♦ EEPROM valdymo registras.

EEPROM skaitymo / rašymo procesas

Registrai, naudojami prieigai prie EEPROM, yra įprasti I / O registrai. Automatinio buvimo vietos nustatymo funkcijos buvimo laikas leidžia vartotojo programai savarankiškai nustatyti momentą, kada galima įrašyti kitą baitą. Jei programoje yra komandos, rašančios į EEPROM, reikia imtis kai kurių atsargumo priemonių.

Maitinimo grandinėse, kuriose įrengtas geras filtras, įjungiant ir išjungiant VCC įtampa lėtai kinta. Tai priverčia prietaisą tam tikrą laiką veikti žemesne įtampa nei minimali leistina tam tikro dažnio dažnio įtampa.

3. I / O jungtys

Visi AVR mikrovaldiklių prievadai skaitmeninio įvesties ir išvesties režime yra pilnaverčiai dvipusiai prievadai, kuriuose kiekvienas išėjimas gali veikti tiek įvesties, tiek išvesties režimais. Tai reiškia, kad kiekvienas atskiras prievado bitas gali būti sukonfigūruotas kaip įvestis arba kaip išvestis, neatsižvelgiant į visų kitų to paties prievado bitų nustatymą.

Galite sukonfigūruoti prievado bitus naudodami iš naujo ir nustatyti SBI bei CBI bitus. Tas pats pasakytina apie vertės pakeitimą išvestyje (jei iškrova sukonfigūruota kaip išėjimas) arba vidinio apkrovos varžos įjungimą / išjungimą (jei iškrova sukonfigūruota kaip įvestis).

Visi šie nustatymai atliekami atskirai kiekvienam prievado kaiščiui. Kiekvieno prievado kaiščio išvesties buferis turi subalansuotą išėjimo pakopą ir didelę apkrovos galią. Bet kurio uosto kiekvieno kaiščio apkrovos pakanka tiesiogiai valdyti LED ekraną.

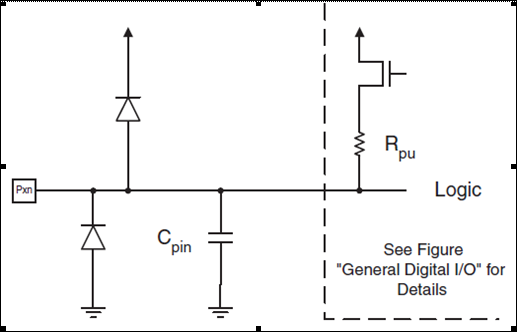

Visi bet kurio uosto kaiščiai turi atskirai sujungtus apkrovos varžus, kuriuos prireikus galima prijungti tarp šio kaiščio ir maitinimo šaltinio. Kiekvienos uosto linijos įvesties grandinės turi du apsauginius diodus, sujungtus su maitinimo grandine ir prie bendro laido, kaip parodyta fig. 7

Fig. 7 - ekvivalentiškos vienos kategorijos įvesties-išvesties įėjimo grandinių grandinės

Raidė „x“ registrų pavadinimų aprašyme reiškia prievado pavadinimą, mažosios raidės „n“ reiškia bitų skaičių. Kai naudojate šį pavadinimą programoje, vietoj šių simbolių turite pakeisti konkrečią prievado pavadinimo raidę ir konkretų bitų numerį.

Pavyzdžiui, PORTB3 - 3 prievado B bitui, jei dokumentuose šis bitas buvo vadinamas PORTxn.

Yra trys specialūs registrai kiekvienam mikrovaldiklio įvesties / išvesties prievadui:

♦ PORTx - duomenų registras;

♦ DDRx - valdymo registras;

♦ PINx - registras, skirtas uosto linijų būsenai tiesiogiai nuskaityti.

Uosto linijos būsenos tiesioginio skaitymo registras yra tik skaitomas, o duomenų registras ir valdymo registras yra ir skaitomi, ir rašomi.

Tačiau taip pat galima parašyti loginį vienetą į bet kurį PINx registro bitą. Tai perjungs atitinkamą duomenų registro bitą (PORTx). Kiekvienas PORTx registro bitas kontroliuoja vidinio apkrovos varžos įjungimą ir išjungimą, jei atitinkamas prievado bitas yra įvesties režime.

3.1 Prievadų naudojimas skaitmeniniam I / O

Kiekviena uosto iškrova yra dvikryptė I / O linija, turinti galimybę sujungti vidinį atsparumą apkrovai. Fig. 8 yra vienos įvesties / išvesties prievado linijos funkcinė schema. Šios linijos išėjimo kontaktas nurodytas „Pxn“ grandinėje.

Fig. 8 - supaprastinta vienos eilutės skaitmeninio įėjimo-išvesties schema

Smeigtuko konfigūracija

Kiekvienas prievado bitas yra susietas su trijų trijų specialiųjų registrų bitais: DDxn; PORTxn; PINxn.

Kaip jau minėta:

♦ DDxn bitas yra DDRx registro bitų skaičius n;

♦ PORTxn bitas yra PORTx registro bitų skaičius n;

♦ PINxn bitas yra PINx registro bitų skaičius n.

DDRx registro DDxn bitas pasirenka atitinkamo bito informacijos perdavimo kryptį. Jei loginis vienetas parašytas DDxn, Pxn bitas veikia kaip išvestis. Jei DDxn parašytas loginis nulis, „Pxn“ bitas veikia kaip įvestis.

Jei prievado bitas sukonfigūruotas kaip įvestis, nustatant PORTxn bitą į vieną įjungiamas vidinis apkrovos rezistorius. Norint atjungti apkrovos varžą, „PORTxn“ reikia loginės nulio. Iškart po sistemos atkūrimo, visų jungčių kaiščiai pereina į trečiąją (didelės varžos) būseną.

Jei prievado bitas sukonfigūruotas kaip išvestis (nustatant PORTxn bitą į vieną), tada šis įrenginys pasirodys prievado išvestyje. Jei bitui PORTxn užrašomas loginis nulis, tada išvestis bus lygi nuliui.

4. Išoriniai pertraukimai

4.1 Tikslas ir darbo režimai

Norėdami iškviesti išorinius pertraukiklius, naudojami įėjimai INT0, INT1 arba bet kuris iš PCINT7-0 įėjimų. Jei įjungiami pertraukimai, jie bus iškviečiami, net jei išėjimai INT0, INT1 ir PCINT7-0 sukonfigūruoti kaip išėjimai.

Ši funkcija suteikia galimybę programiškai generuoti pertraukimus. PCI1 pertraukimas yra signalo pakeitimo pertraukimas bet kuriame iš pint7-8 kaiščių. PCI0 pertraukimas yra bet kokio PCINT7-0 signalo pakeitimo pertraukimas. Be to, tiek PCI1 pertraukimui, tiek PCI0 pertraukimui bet kuris iš jam priskirtų įėjimų gali būti savavališkai pašalintas iš veikimo.

Valdymo registrai PCMSK1 ir PCMSK0 nustato, kuris iš įėjimų sukels atitinkamą pertraukimą. Keitimas nutraukia kaiščius. PCINT7-0 veikia asinchroniškai. Todėl šio tipo pertraukimas gali būti naudojamas pabudimui iš visų miego režimų, išskyrus laukimo režimą.

Nutraukus INT0 ir INT1 palaikomi keli režimai. Jie gali būti vadinami kylančiu kraštu, krintančiu kraštu arba žemo loginio lygio statiniu signalu. Vienas iš šių režimų pasirenkamas naudojant išorinį trikdžių valdymo registrą - EICRA.

Įjungus vieną iš INT0 arba INT1 pertraukimų ir sukonfigūravus kaip žemą įvesties lygio pertraukimą, pertraukimo užklausa bus generuojama visą laiką, o įėjimo mažai.

Nutraukimai INT0 ir INT1 vadinami mažiausiai asinchroniškai. Tai reiškia, kad toks pertraukimas gali būti naudojamas pabudimui iš bet kurio miego režimo, išskyrus laukimo režimą.

Mikrovaldiklio paleidimo laikas nustatomas naudojant saugiklių jungiklius SUT ir CKSEL.

5. Aštuonių bitų laikmatis / skaitiklis su palaikymu PWM režimui

5.1 Tikslas ir ypatybės

Laikmatis / skaitiklis T0 yra universalus aštuonių bitų skaitiklio modulis su dviem nepriklausomais sutapimo moduliais ir su PWM palaikymu. Tai leidžia suformuoti nurodytus laiko intervalus (darbui realiu laiku). Jis taip pat gali tarnauti kaip periodinių signalų generatorius.

Apsvarstykite pagrindines laikmačio / skaitiklio savybes.

5.2 Supaprastinta blokinė schema

Aštuonių skaitmenų laikmačio / skaitiklio supaprastinta blokinė schema parodyta fig. 9. Centrinės šerdies registrai ir duomenų perdavimo grandinės diagramoje parodyti paryškintomis linijomis.

Fig. 9 - 8 bitų laikmačio / skaitiklio blokinė schema

5.3 Registrai

Tiek skaičiavimo laikmačio / skaitiklio registras (TCNT0), tiek abu atitikmenų registrai (OCR0A ir OCR0B) yra aštuonių bitų registrai. Nutraukimo reikalavimo buvimas (10 pav. Jis sutrumpintai vadinamas „skambučio pertraukimas“) visada gali būti nustatomas pagal būseną, atitinkančią pertraukimo vėliavą TIFR registre.

Kiekvienas pertraukimas gali būti atskirai užmaskuotas naudojant TIMSK laikmačio pertraukimo kaukės registrą. TIFR ir TIMSK registrai fig. 9 nerodomi.

Laikmatis / skaitiklis gali veikti tiek iš vidinio laikrodžio per paskirstytuvą, tiek iš išorinio laikrodžio įėjimo į T0. Laikrodžio šaltinio parinkimo grandinė perduoda pasirinkto šaltinio laikrodžio impulsus į laikmačio / skaitiklio įvestį, o kiekvienas šio signalo impulsas padidina (arba sumažina) jo vertę.

Jei nepasirenkamas laikrodžio šaltinis, laikmatis / skaitiklis sustoja.

Signalas, esantis laikrodžio šaltinio pasirinkimo grandinėje (clkT0), yra vadinamas laikmačio sinchronizacijos signalu.

OCR0A ir OCR0B registrų turinys yra nuolat lyginamas su laikmačio / skaitiklio verte. Palyginimo rezultatą generatorius gali panaudoti generuodamas PWM signalą arba kintamo dažnio stačiakampius impulsus vienoje iš išėjimų OC0A arba OC0B.

Atsitiktinumo metu vienas iš kanalų nustato atitinkamą vėliavą OCF0A arba OCF0B, kurios gali būti naudojamos generuoti prašymą nutraukti sutapimą.

5.4 Naudoti simboliai

Apibūdinant skaitiklius, visoms svarbioms būsenoms naudojamas specialus žymėjimas. Šie žymėjimai pateikti lentelėje. 1.

8 bitų skaitiklio pagrindinių būsenų simboliai

1 lentelė

5.5 Sąskaitos modulis

Aštuonių skaitmenų laikmačio / skaitiklio pagrindas yra programuojamas grįžtamasis skaitiklio modulis. Fig. 10 parodyta skaičiavimo modulio ir jo valdymo signalų blokinė schema.

Fig. 10 - skaičiavimo modulio blokinė schema

Apsvarstykite vidinius signalus:

♦ skaičius - padidina arba sumažina TCNT0 kiekį 1;

♦ kryptis - pasirinkimas tarp mažinimo ir didinimo;

♦ išvalyti - išvalyti TCNT0 (visus bitus nustatykite į nulį);

♦ clkT0 - laikmačio / skaitiklio laikrodžio dažnis;

♦ viršuje - atsiranda pasiekus TCNT0 maksimali vertė;

♦ dugnas - atsiranda, kai TCNT0 pasiekia savo mažiausią vertę (nulį).

Atsižvelgiant į laikmačio veikimo režimą, kiekvienas laikrodžio impulsas (clkT0) išvalo, padidina arba sumažina skaitiklio vertę. „ClkT0“ signalą galima priimti iš išorinio arba vidinio laikrodžio šaltinio. Tai lemia laikrodžio pasirinkimo bitai (CS02: 0). Kai nepasirenkamas laikrodžio šaltinis (CS02: 0 \u003d 0), laikmatis sustoja.

Centrinis procesorius gali pasiekti TCNT0 registro vertę, nepaisant to, ar yra „clkT0“ signalas, ar ne. Centrinio procesoriaus rašymo komanda turi pirmenybę prieš visas kitas operacijas (priešingo valymo ar skaičiavimo operacijas).

Laikmačio režimai nustatomi nustatant TCCR0A registro bitus WGM01 ir WGM00, o TCCR0B registro WGM02 bitus. Tarp pasirinkto skaitiklio veikimo režimo ir signalo dažnio esant OC0A išėjimui yra glaudus ryšys.

Laikmačio / skaitiklio perpildymo vėliava (TOV0) nustatoma pagal darbo režimą, parinktą naudojant bitus WGM01: 0. TOV0 vėliava gali būti naudojama generuoti procesoriaus pertraukimus.

5.6 Rungtynių modulis

Modulis remiasi aštuonių bitų palyginikliu, kuris nuolat lygina TCNT0 registro turinį su kiekvieno iš dviejų atitikmenų registrų (OCR0A arba OCR0B) turiniu. Kiekvieną kartą, kai TCNT0 turinys yra lygus OCR0A arba OCR0B turiniui, komparatorius sukuria atitikties signalą. Šis signalas nustato atitinkamą atitikties vėliavą (OCF0A arba OCF0B) kitame laikrodžio cikle.

Jei įjungtas tinkamas pertraukimas, nustatant atitikties vėliavą įvyksta pertraukimas. Rungtynių vėliava automatiškai atstatoma, kai prasideda pertraukimo apdorojimo rutina. Vėliavą taip pat galima išvalyti programiškai, įrašant į ją loginį vienetą.

Esant dažnio generatoriaus režimui, atitikties signalas naudojamas rungtynių išvesties signalui generuoti ir naudojamas išvesties signalui generuoti pagal pasirinktą darbo režimą, kurį nustato WGM02: 0 bitai, taip pat palyginimo režimo pasirinkimo bitus (COM0x 1: 0). Kai kuriais atvejais dažnio generatorius naudoja maksimalius ir apatinius signalus, kad gautų kritines vertes atskirais darbo režimais. Fig. 11 parodyta atitikimo modulio blokinė schema. Paveiksle raidė x yra simbolis. Skirtingiems sutapimo moduliams x yra A arba B.

Fig. 11 - rungtynių modulio blokinė schema

OCR0x registrai turi dvigubą buferį bet kuriame impulsų pločio moduliacijos (PWM) režime. Normaliame ir STS režime (Atstatyti sutapimo metu) dvigubas buferizavimas yra išjungtas. Dvigubas buferizavimas sinchronizuoja momentą, kai OCR0x registras atnaujinamas, kai laikmatis pasiekia viršutinę arba apatinę ribas. Sinchronizacija neleidžia atsirasti asimetrinių PWM impulsų, tai yra, impulsų, kurių ilgis yra lygus nelyginiam laikrodžio ciklų skaičiui. Tai užtikrina aukštos kokybės PWM signalus.

Prieiga prie OCR0x registro gali atrodyti pernelyg sudėtinga. Iš tikrųjų taip nėra. Jei įjungtas dvigubas buferizavimas, procesorius prie buferio prieina prie OCR0x registrų. Jei buferizavimas neleidžiamas, centrinis procesorius tiesiogiai prieina prie OCR0x registrų.

5.7 Priverstinis rungtynių išėjimo būsenos pasikeitimas

Visuose ne PWM laikmačio režimuose bet kurio sutapimo išėjimo signalą galima priverstinai pakeisti įrašant vienetą į specialųjį bitą FOC0x. Priverstinis rungtynių išvesties pakeitimas nenustato OCF0x vėliavos ir neperkrauna laikmačio.

Signalas, esantis „OC0x“ išvestyje, pasikeis taip pat, kaip ir realios atitikties atveju. T. y., OC0x išvesties elgsena priklausys nuo COM0x1: 0 bitų nustatymo. Priklausomai nuo šių bitų vertės, išvesties signalas bus nustatytas į vieną arba atstatytas į nulį arba pakeis jo reikšmę į priešingą pusę.

5.8 Blokuokite atitikimo režimą, kai rašote TCNT0

Kai vertė įrašoma į TCNT0 registrą, palyginimo operacija blokuojama vienam laikmačio įvesties signalo laikrodžio ciklui. Tai atsitinka net sustabdžius laikmatį. Ši savybė leidžia įrašyti į OCR0x registrą tą pačią vertę, kaip ir į TCNT0 registrą, nesukeliant trikdžių, kai įvedamas laikmačio signalo laikmatis / skaitiklis.

5.9 Naudokite pertraukimo modulį

Kaip jau minėta, bet kuriame laikmačio veikimo režime įrašant TCNT0 registrą, palyginimo modulio veikimas sustabdomas vienam laikrodžio signalo laikotarpiui. Tai gali sukelti klaidų keičiant TCNT0 registro turinį, nepriklausomai nuo to, ar veikia laikmatis / skaitiklis, ar ne.

Jei TCNT0 įrašyta vertė yra lygi OCR0x įrašytai vertei, palyginimo operacija praleidžiama, o tai lems netinkamą laikmačio veikimą dažnio generatoriaus režime.

Dėl tos pačios priežasties neįmanoma parašyti TCNT0 vertės, lygios BOTTOM, kai skaitiklis veikia atgalinės atskaitos režimu.

OC0x išvesties darbo režimai turi būti sukonfigūruoti prieš atitinkamos prievado linijos konfigūravimą kaip išvestį. Lengviausias būdas įdiegti norima vertė esant OC0x išėjimui - naudokite priverstinį diegimą (bitą FOC0x) normaliame režime. OC0x registrai išlaiko savo vertę perjungdami signalo generavimo režimus.

5.10 Derinkite išvesties modulį

Bitai COM0x1: 0 atlieka dvi funkcijas. Dažnių generatorius naudoja bitus COM0x1: 0, kad nustatytų, kaip keičiasi atitikties modulio išvesties signalas (OC0x), kai jis nustato atitiktį. Tuo pačiu metu COM0x1: 0 bitai kontroliuoja signalo šaltinį OC0x išvestyje.

Fig. 12 yra supaprastinta schema, rodanti COM0x1: 0 bitų veikimo logiką.

Fig. 12 - suderinkite išėjimo grandinę

Kaip matote iš paveikslėlio, reikšmė COM0x1: 0 turi įtakos mikroschemos įvesties / išvesties prievado būklei, neatsižvelgiant į pagrindinius šio uosto valdymo registrus (DDR ir PORT). Be to, kai kalbame apie OC0x būseną, turime suprasti, kad vidinis OC0x registras nėra tas pats, kas OC0x lusto kontaktas. Iškart po sistemos atstatymo, OC0x registre užrašomas nulis.

Jei yra nustatytas kuris nors iš COM0x1: 0 bitų, pagrindinė I / O prievado funkcija atšaukiama, o atitikties signalas (OC0x) iš dažnio generatoriaus pereina į išėjimą. Tuo pačiu metu OC0x kontaktinės informacijos (įvesties ar išvesties) perdavimo kryptis vis dar priklauso nuo atitinkamo DDR registro bitų.

Bito, nustatančio OC0x išėjimo informacijos perdavimo kryptį, vertė, jei ji turėtų veikti kaip išėjimas, turi būti nustatyta prieš tai, kai OC0x registro vertė pasiekia šią išvestį. Alternatyvios uosto funkcijos nepriklauso nuo signalo generatoriaus veikimo būdo.

5.11 Veikimo režimai

Veikimo režimą, tai yra laikmačio / skaitiklio elgseną ir sutapimo signalo išvestį, lemia tiek signalo generatoriaus veikimo režimas (WGM02: 0), tiek sutapimo signalo išvesties režimas (COM0x1: 0). Bitų, nustatančių atitikties signalo išėjimo režimą, būsena neturi įtakos skaičiavimo sekai, kurią lemia tik signalo generatoriaus konfigūracijos bitų būsena.

Bitai COM0x1: 0 nustato, ar PWM išėjimo signalas turi būti apverstas, ar ne (apverstas, ar ne apverstas PWM). Režimams, kurie nėra PWM, COM0x1: 0 bitų turinys nustato, ar išvesties signalas sutapimo momentu turėtų būti nustatytas į vieną, atstatyti į nulį ar perjungti į priešingą būseną.

5.12 Įprastas režimas

Įprastas režimas (WGM02: 0 \u003d 0) yra lengviausias laikmačio režimas. Šiame režime skaičiavimo kryptis visada yra į priekį (turinys didėja), o skaitiklis nėra priverstas iš naujo nustatyti. Skaitiklis tiesiog perpildomas, kai pasiekia daugiausiai aštuonių skaitmenų (TOP \u003d 0xFF), o tada pirmiausia paleidžiamas iš naujo (0x00).

Įprasto darbo metu laikmačio / skaitiklio perpildymo vėliava (TOV0) bus nustatyta, kai TCNT0 taps lygus nuliui. Šiuo atveju „TOV0“ vėliava elgiasi kaip devintasis bitas, išskyrus tuos atvejus, kai ji tik nustatyta, bet ne iš naujo nustatyta.

Naudodamiesi laikmačio perpildymo pertraukimu, kuris automatiškai išvalo TOV0 vėliavą, galite padidinti programos konvertavimo koeficientą. Įprastas režimas neturi jokių funkcijų, į kurias turėtumėte sutelkti dėmesį. Naują skaičiavimo registro vertę galima bet kada įrašyti.

Atitikimų modulis kartais gali būti naudojamas skambinti pertraukėliams. Nerekomenduojama naudoti atitikties signalo, norint generuoti signalus įprastu režimu, nes tai labai sulėtins procesorių.

5.13 Rungtynių atkūrimas (STS)

Atstatymo režime, kai sutampa, arba, kitaip tariant, STS režime (kai WGM02: 0 \u003d 2), OCR0A registras yra naudojamas skaitiklio konvertavimo koeficientui valdyti. STS režime skaitiklis atstatomas iki nulio, kai registrų skaitiklio (TCNT0) ir OCR0A registro turinys sutampa.

Taigi registre OCR0A nustatoma didžiausia skaitiklio vertė, taigi ir jo perskaičiavimo koeficientas.

Šis režimas leidžia valdyti signalo dažnį modulio išvestyje. Taip pat supaprastintas išorinių įvykių skaičiavimas. Registro skaitiklio (TCNT0) vertė didėja, kol tarp TCNT0 ir OCR0A nesutampa, o tada skaitiklio (TCNT0) turinys bus išvalytas.

Pertraukimas gali būti iškviečiamas kiekvieną kartą, kai skaitiklis pasiekia aukščiausią reikšmę. Tokiu atveju naudojamas flagOCF0A. Jei pertraukimas įjungtas, iškviečiamas pertraukimo apdorojimo rutina, kuri gali būti naudojama atnaujinti TOP reikšmę.

„TOP“ nustatymas yra per arti BOTTOM vertės tuo metu, kai skaitiklis neveikia arba esant mažam preliminaraus padalijimo koeficientui, jis turi būti atliekamas atsargiai, nes STS režimas neturi dvigubo buferio.

Jei nauja OCR0A įrašyta vertė yra mažesnė už dabartinę TCNT0 vertę, šaltinis praleidžia sutapimo momentą. Dėl to skaitiklis ir toliau bus skaičiuojamas iki didžiausios jo vertės (0xFF), tada jis peržengs nulį ir tik tada įvyks sutapimo momentas.

Norint generuoti išėjimo signalą STS režimu, OC0A išvestį kiekvieną kartą sutapimo metu galima nustatyti į išėjimo lygio perjungimo režimą. Norėdami tai padaryti, nustatykite sutapimo signalo išvesties režimo bitus (COM0A1: 0 \u003d 1) į reikiamą padėtį. OC0A registro reikšmė nebus perduota atitinkamam išorinio uosto kontaktui, jei jis nėra sukonfigūruotas kaip išėjimas. Sukurtas signalas turės maksimalų dažnį fOC0 \u003d fclk_I / O / 2, kai nulis (0x00) bus įrašytas į OCR0A registrą. Signalo dažnį galima apskaičiuoti pagal šią lygtį:

kur kintamasis N yra preliminaraus padalijimo koeficientas (1, 8, 64, 256 arba 1024).

Kaip ir normaliame režime, TOV0 vėliava nustatoma kiekvieną kartą, kai skaitiklis suskaičiuojamas iki MAX ir nueinamas į nulį.

5.14 „FastPWM“ režimas (greitasis PWM)

Mikrovaldiklis turi keletą impulsų pločio moduliavimo (PWM) režimų. Anglų kalba tai skamba kaip impulso pločio moduliavimas (PWM) .Spartus PWM pasirenkamas naudojant WGM02: 0 \u003d 3 arba 7. Šiame režime generuojamas aukščiausio dažnio PWM signalas. Greitasis PWM skiriasi nuo kitų PWM režimų tuo, kad generuojant signalą skaitiklis sukuria tik amžiaus seką. Tai yra, skaitiklio vertės pokytis turi pjūklo signalo formą su vienpusiu nuolydžiu.

Skaičiavimas prasideda verte BOTTOM ir baigiasi verte TOP. Po to skaitiklis paleidžiamas iš naujo (vertė BOTTOM vėl nustatoma). TOP vertė yra 0xFF, kai WGM2: 0 \u003d 3.

Jei WGM2: 0 \u003d 7, TOP vertė nustatoma pagal OCR0A registro turinį. Neapversto išėjimo režime sutapimo signalas (OC0x) atstatomas, kai sutampa TCNT0 ir OCR0x vertės ir įvyksta perėjimas prie BOTTOM.

Invertuojant, išėjimo signalas nustatomas sutapimo ir perėjimo į BOTTOM momentu. Dėl to, kad skaitiklis visada veikia tik viena kryptimi, signalo dažnis greitame PWM režime gali būti dvigubai didesnis nei fazių teisingo PWM režimo metu, kai naudojamas pjūklo signalo signalas dviem šlaitais.

Dėl aukšto išėjimo signalo dažnio greitasis PWM režimas puikiai tinka kuriant galios valdymo sistemas, statant lygintuvus ir skaitmeninio-analoginio keitiklius. Aukštas dažnis leidžia naudoti mažus išorinius komponentus (ritinius, kondensatorius) ir taip sumažinti visas sistemos sąnaudas.

Greitame PWM režime skaitiklio vertė padidėja, kol ji pasiekia aukščiausią reikšmę. Kitame laikmačio laikrodžio cikle skaitiklis išvalomas.

Laikmačio / skaitiklio perpildymo vėliava (TOV0) nustatoma kiekvieną kartą, kai skaitiklis pasiekia aukščiausią reikšmę. Jei pertraukimas įjungtas, iškviečiama pertraukimo apdorojimo rutina, kurią galima naudoti atnaujinant atitikties lygį.

Greitame PWM režime suderinamas modulis yra naudojamas generuoti PWM signalą OC0x išėjimuose. Nustatę COM0x1: 0 \u003d 2 bitus, išvestyje generuosite ne apverstą PWM signalą. Norint generuoti apverstą PWM signalą, būtina nustatyti COM0x1: 0 \u003d 3. Nustatant bitus COM0A1: 0 \u003d 1, signalas, esantis AC0A išvestyje sutapimo momentu, persijungia į priešingą būseną, su sąlyga, kad bitas WGM02 \u003d 1.

Ši parinktis negalima naudojant OC0B išvestį. Tikroji OC0x vertė pateks į lusto išorinį kontaktą tik tuo atveju, jei jis sukonfigūruotas kaip išėjimas.

PWM signalas generuojamas nustatant (iš naujo nustatant) OC0x registrą tuo metu, kai OCR0x ir TCNT0 vertės sutampa, ir iš naujo nustatant (nustatant) šį registrą pirmame laikrodžio cikle, po to, kai skaitiklis atstatytas (keičiant jo vertę iš TOP į BOTTOM). PWM signalo dažnį išvestyje galima apskaičiuoti naudojant šią išraišką:

Kintamasis N nurodo preliminaraus padalijimo koeficientą (1, 8, 64, 256 arba 1024). Atskirai reikia atsižvelgti į kelis atvejus, kai generuojamas PWM signalas, kai reikšmė, artima ribai, įrašoma į OCR0A registrą.

Jei OCR0A registras yra nustatytas kaip BOTTOM, tada kiekvieno MAX + 1 laikmačio ciklo išvestis bus trumpa.

Jei MAX reikšmė bus įrašyta į OCR0A registrą, tai išvestyje turės aukštą arba žemą loginį lygį (priklausomai nuo bitų COM0A1: 0 vertės).

Išėjimo signalo dažnis greitame PWM režime (esant 50% valdymo lygiui) gali būti pasiektas, jei OC0x registras yra priverstas perjungti savo logikos lygį kiekvienose rungtynėse (COM0x1: 0 \u003d 1).

Tokiu būdu sugeneruoto signalo maksimalus dažnis bus fOC0 \u003d fclk_I / O / 2, kai OCR0A registre užrašoma nulis. Ši savybė leidžia jums OCR0A registrą perjungti taip pat, kaip ir STS režimu, tačiau tuo pat metu visiškai išnaudokite dvigubo buferio, kuris naudojamas greitame PWM režime, pranašumus.

5.15 „PWM“ fazė teisinga („PhaseCorrectPWM“)

Fazių teisingas PWM režimas (WGM02: 0 \u003d 1 arba 5). PWM signalas generuojamas naudojant didelį perskaičiavimo koeficientą ir yra teisingas fazėje. Fazių teisingumas užtikrinamas dėl skaitiklio veikimo pjūklų režimu su dvipusiu pakreipimu.

Skaitiklis periodiškai keičia savo sąskaitos kryptį. Pirmiausia jis skaičiuojamas nuo BOTTOM iki TOP, tada pasikeičia sąskaitos kryptis, o skaitiklis skaičiuoja TOP iki BOTTOM. Tada vėl pasikeičia pasakojimo kryptis ir viskas vėl kartojama.

Aukščiausia WGM2 vertė yra 0xFF: 0 \u003d 1 ir nustatoma pagal OCR0A registrą WGM2: 0 \u003d 5.

Neįeinantis išvesties režimas, OCR0x išvesties signalas atstatomas iki nulio, kai sutampa TCNT0 ir OCR0x registrų turinys, jei skaitiklis dirba pirmyn (padidinti). Jei skaitiklis sumažėja, sutapimo metu vertė nustatoma viena.

Apverstos išvesties režimu vaizdas atvirkštinis. Dviejų krypčių pakreipimo režimui būdingas mažesnis maksimalus išėjimo dažnis, palyginti su ankstesniu atveju, kai pjūklas naudojamas su pakreipimu iš vienos pusės. Dėl fazių simetrijos su dvipusiu pakreipimu, tokiems režimams teikiama pirmenybė kuriant variklio valdymo sistemas.

Fazių teisingu PWM režimu skaitiklio vertė padidėja, kol pasieks aukščiausią reikšmę. Kai skaitiklis pasieks TOP, skaičiavimo kryptis pasikeis. TCNT0 turinys bus populiariausias vieną laikmačio periodą. Laikmačio / skaitiklio perpildymo vėliava (TOV0) nustatoma kiekvieną kartą, kai skaitiklis pasiekia BOTTOM reikšmę. Pertraukimo vėliava gali būti naudojama generuoti nutraukimo užklausą. Toks pertraukimas bus atliekamas kiekvieną kartą, kai skaitiklio turinys pasieks BOTTOM reikšmę.

Esant teisingam PWM režimui, atitikties modulis yra naudojamas generuoti PWM signalą, esant OC0x išėjimui. Nustatant COM0x1 bitus: 0 \u003d 3. Nustačius COM0A0 \u003d 1 bitus, signalas, esantis OC0A išvestyje, kiekvieną kartą sutapimo momentu yra apverčiamas, jei nustatytas WGM02 bitas. Ši parinktis negalima naudojant OC0B išvestį. Faktinė OC0x vertė išvedama į išorinį uosto kaištį tik tuo atveju, jei ji sukonfigūruota kaip išvestis.

PWM signalas generuojamas iš naujo nustatant (nustatant) OC0x tuo metu, kai OCR0x ir TCNT0 registrų turinys sutampa, kai skaitiklis dirba, kad padidėtų, ir yra nustatytas (atstatomas) sutapimo metu, jei skaitiklis veikia, kad sumažėtų. PWM išėjimo signalo dažnis fazių teisingu PWM režimu gali būti apskaičiuojamas pagal šią formulę:

Kai kintamasis N reiškia preliminaraus padalijimo koeficientą (1, 8, 64, 256, 1024).

Ypatingos atvejai yra kraštutinės OCR0A registro vertės, kai generuojami PWM signalai fazių teisingu PWM režimu. Neįeinantis režimas, kai rašote į OCR0A registrą, BOTTOM reikšmė išvestyje nustatoma žemai logikos lygiui. Kai MAX vertė įrašoma į OCR0A, loginis vienetas nustatomas išvestyje. Apversimo režimui išėjimo signalas turės priešingas vertes.

6. Komandų sistemos aprašymas

6.1 Komandų sistema. Komandų sistemos apžvalga

AVR šeimoje - mikrovaldiklio valdymo sistema skirtingos rūšys yra nuo 89 iki 130 komandų. 2323, 2343, 2313, 4433, 8515 ir 8535 tipo mikrovaldikliams komandų sistemą sudaro 118 komandų. Ši komandų sistema bus vadinama baze.

Lentelėje. 2.1 - 2.13 aprašomos operacijos, kurias atlieka pagrindinės sistemos komandos, ir pateikiami komandų, naudojamų kuriant programą, mnemoniniai kodai AVR montuotojo kalba. Lentelės pateikia nenutrūkstamą komandų, naudotų vėliau tekste, numeravimą.

Pagrindinę komandų sistemą sudaro:

▪ 33 registravimo operacijų komandos, kurioms atlikti naudojami tik bendrosios paskirties registrai (komandos Nr. 1-33);

▪ 26 komandos, turinčios adresą SRAM adresų erdvėje (komandos Nr. 34-59);

▪ 2 komandos, turinčios prieigą prie I / O registrų (komandos Nr. 60 ir 61);

▪ 1 komanda, turinti prieigą prie „FlashROM“ (komandos numeris 62);

▪ 22 operacijų komandos, kurių bitai yra bendrųjų ir įvesties-išvesties registrų bitai (komandos Nr. 63-84);

▪ 34 komandos, kontroliuojančios programos eigą (komandos Nr. 85-118).

Mikrovaldiklių, tokių kaip t11, t12, t15, 1200 ir t28, kurie neturi SRAM, komandų sistema neapima komandos, kurios adresuoja adresą SRAM adresų erdvėje, išskyrus komandas su mnemoniniais kodais LDRd, Z (Nr. 40) ir STZ, Rr (Nr. 41), kurie naudojami nuorodoms į bendruosius registrus ir įvesties-išvesties registrus naudojant netiesioginį adresų skyrimą. Šių mikrovaldiklių valdymo sistema taip pat neapima 2 registravimo operacijų komandų (Nr. 32 ir 33) ir dviejų programų valdymo komandų (Nr. 86 ir 88). 1200 tipo mikrovaldikliams komandų sistema taip pat neapima komandos, turinčios prieigą prie „FlashROM“, o m163 tipo mikrovaldikliams, be to, ji turi aparatūros daugiklį.

(PC) + 1 → STACK

(STACK) → AK

(STACK) → AK

12 lentelė

| № | Būklė | Komandos mnemonika | № | Būklė | Komandos mnemonika |

| 91 | I \u003d 0 | BRID k | 92 | I \u003d 1 | BRIEJAS k |

| 93 | T \u003d 0 | BRTC k | 94 | T \u003d 1 | BRTS k |

| 95 | H \u003d 0 | BRHC k | 96 | H \u003d 1 | BRHS k |

| 97 | S \u003d 02. (X) + 1 → X | BRGE k | 98 | S \u003d 1 | BRLT k |

| 99 | V \u003d 0 | BRVC | 100 | V \u003d 1 | BRVS k |

| 101 | N \u003d 0 | BRPL k | 102 | N \u003d 1 | BRMI k |

| 103 | Z \u003d 0 | BRNE k | 104 | Z \u003d 1 | Breq k |

| 105 | C \u003d 0 | BRCC k | 106 | C \u003d 1 | BRCS k |

| 107 | C \u003d 0 | BRSH k | 108 | C \u003d 1 | BRLO k |

| 109 | SREG.b \u003d 0 | BRBC b, k | 110 | SREG.b \u003d 1 | BRBS b, k |

| k \u003d -64 - +63; b \u003d 0 - 7 | |||||

13 lentelė

14 lentelė

| № | Operacija | Komandos mnemonika |

| 116 | MK → energijos taupymo režimas | Miegoti |

| 117 | Iš naujo paleiskite WDT | Wdr |

| 118 | Ne | Nop |

6.3 Registravimo operacijų komandos

Į registrų operacijų grupę įeina perkėlimo, aritmetinės ir loginės operacijos. Komandų registravimo operacijos aprašytos lentelėje. 2, 3 ir 4 Visų registrų operacijų komandų mašinų kodai yra „žodžio“ formato, komandos Nr. 1–31 vykdomos vienu laikrodžio ciklu, o komandos Nr. 32 ir 33 vykdomos dviem laikrodžio ciklais.

Aritmetines operacijas - sudėti ir atimti - galima atlikti nepaženklintais skaičiais dvejetainiame kode ir pasirašytais skaičiais pasirenkamame dvejetainiame kode. AVR šeimos mikrovaldikliuose, skirtingai nei daugelio kitų šeimų mikrovaldikliuose, kuriuose atimama sumažinant iki sudėjimo su skaičiumi su pakeistu ženklu (X - Y \u003d X + (-Y)), atėmimas atliekamas naudojant aparatūros dvejetainį atimtį.

Atliekant aritmetines ir logines operacijas, be rezultato kodo, sukuriamos rezultato charakteristikų reikšmės. Atliekant palyginimo operacijas (komandos Nr. 18, 19 ir 27) generuojamos tik rezultato atributų vertės.

Rezultatų atributų reikšmes rodo SREG būsenos registro bitų būsena (Nr. 33FF). Naudojamos šešios rezultato charakteristikos, kurioms priskiriami pavadinimai C (SREG.0), Z (SREG.1) N (SREG.2), V (SREG.3, S (SREG.4) ir H (SREG.5). 2.1 - 2.3 ženklai, kurių reikšmės susidaro vykdant komandas, yra pažymėti „+“ ženklu arba nurodomas jų pavadinimas.

Atliekant skirtingas operacijas, charakteristikų vertė formuojama pagal skirtingas taisykles.

C ženklas turi vieną reikšmę:

▪ kai papildomos operacijos metu atsiranda aukšto rango perdavimo vienetas (komandos Nr. 14, 15 ir 32);

▪ kai papildomos operacijos metu paskolos vienetas pasirodo vyresnio amžiaus kategorijoje (komandos Nr. 4, 16, 17, 18, 19, 25, 26, 27 ir 33);

▪ kai pamainos metu įrenginys peržengia bitų tinklelio ribas (komandos Nr. 7, 8, 9, 10 ir 11).

Viena atributo C reikšmė pridėjimo ir atėmimo operacijų metu su neparašytais skaičiais rodo, kad gautas neteisingas operacijos rezultatas dėl bitų tinklelio perpildymo.

Gaunant nulinį operacijos rezultatą, ženklas Z užima vieną vertę. Atliekant atimties operaciją, atsižvelgiant į paskolą (komandos Nr. 17, 19 ir 26) Z \u003d 1, jei atlikus šią ir ankstesnes operacijas buvo gautas nulinis rezultatas.

N ženklas turi reikšmę, lygią rezultato kodo aukščiausios eilės vertei. Atliekant aritmetines operacijas su pasirašytais skaičiais ir nesant perpildytos bitų tinklelio, tai reiškia rezultato ženklą.

V simptomas turi vieną vertę, jei atliekant aritmetines operacijas su skaičiais su ženklu įvyksta bitų tinklelio perpildymas.

Ženklas S \u003d NV žymi rezultato ženklą atlikdamas aritmetines operacijas su pasirašytais skaičiais, nepriklausomai nuo bitų tinklelio perpildymo. Kai bitų tinklelis yra perpildytas (V \u003d 1), rezultato ženklas yra priešingas reikšmei, esančiai aukšta rezultato kodo tvarka.Ženklas H įgauna vieną reikšmę, jei atimant operaciją yra perdavimo blokas iš D3 į D4, o kai vienetas perkeliamas iš D3 į D4, kai kodo operacija atliekama į kairę.

6.4 Komandos, kuriomis naudojasi SRAM

Nurodymai, adresuojantys adresą SRAM adresų erdvėje, atliekami baitui perduoti (nukopijuoti) tarp bendrojo registro ir elemento, kurį atitinka adresas SRAM adresų erdvėje. Toks elementas gali būti bendrosios paskirties registras (adresai nuo 00 USD iki 1F), įvesties ir išvesties registras (adresai nuo 20 USD iki 5F), atminties vieta SRAM (adresai nuo 60 USD iki maksimalaus adreso SRAM), atminties vieta ERAM (adresai). nuo maksimalaus adreso SRAM +1 iki maksimalaus adreso ERAM).

Komandos su prieiga prie adresų SRAM adresų erdvėje aprašytos 4 lentelėje. 2.4 ir 2.5.

Komandų Nr. 34 ir 35 automatiniai kodai yra „2 žodžių“ formatu, kitų komandų automatiniai kodai yra „žodžio“ formatu. Komandos vykdomos dviem ciklais, o prisijungiant prie ERAM langelių - 3 ciklais. Prireikus prie komandos vykdymo ciklo prisijungiant prie ERAM galima įvesti papildomą laukimo ciklą.

2.4 ir 2.5 lentelėse naudojami šie nauji žymėjimai:

▪ CELL - bendrosios paskirties registras, įvesties ir išvesties registras, atminties ląstelė SRAM, atminties ląstelė ERAM, kuri prieinama naudojant adresą A iš SRAM adresų erdvės;

▪ (Ląstelė) - baitas langelyje;

▪ X, Y, Z - atitinkamai bendrosios paskirties registrų pora X (R26, R27), Y (R28, R29), Z (R30, R31);

▪ (X), (Y), (Z) - žodis atitinkamai registrų X, Y, Z poroje;

▪ STACK - langelis, į kurį patenkama naudojant registre saugomą adresą - SP krūvos rodyklė;

▪ (STACK) - baitas STACK, e;

▪ (SP) - numerio kodas SP registre.

34 ir 35 komandose vykdomas tiesioginis adresavimas. Baito adresas (A \u003d k) nurodomas komandos kode.

Komandose Nr. 36 - 57 įgyvendinamas netiesioginis adresavimas. Baitinis adresas yra X, Y arba Z registrų poroje. Vykdant komandas Nr. 48–53, prieš perduodant, adresas registrų poroje aparatinės įrangos sumažinamas vienu. Vykdant komandas Nr. 54 - 57, adresas, į kurį skambinama, yra lygus adresų, esančių Y arba Z registrų poroje, padidinta q, nurodytu komandos kode. Adresas registrų poroje nesikeičia.

Komandose Nr. 58 ir 59 kodo, esančio kamino registre, adresas naudojamas kaip kodas. Kai mikrovaldiklis įsijungia, rietuvės rodyklėje įvedamas skaičiaus kodas 0. Normaliam rietuvės veikimui, rietuvės kodas programos pradžioje turi įvesti kito skaičiaus kodą. Paprastai aukščiausias adresas SRAM naudojamas kaip toks skaičius. Pavyzdžiui, 8515 tipo mikrovaldikliui šis adresas yra 025F USD.

6.5 Komandos, turinčios prieigą prie I / O registrų

Komandomis, turinčiomis prieigą prie I / O registrų, vykdomos operacijos baitui perkelti (nukopijuoti) iš bendrosios paskirties registro į I / O registrą, naudojant jo numerį ($ 00 - 3F), kad būtų galima pasirinkti I / O registrą. Komandos, turinčios prieigą prie įvesties / išvesties registrų, aprašytos 4 lentelėje. 6. Mašinų instrukcijų kodai yra žodžių forma. Komandos vykdomos vienu laikrodžio ciklu.

Lentelėje. 6 naudojami šie nauji pavadinimai:

▪ PrP - įvesties ir išvesties registras su numeriu P;

▪ (PrP) - baitas PrP registre.

Rašant komandos mnemoniką vietoj konkretaus registro numerio, gali būti naudojamas jos simbolinis pavadinimas. Visi I / O registrai turi įprastus pavadinimus. Skirtingų tipų mikrovaldikliams to paties pavadinimo I / O registrai gali turėti skirtingus pavadinimus. Registruojant vardų pavadinimus mnemoniniais kodais, vietoj jų skaičiaus, šio tipo mikrovaldikliui reikia naudoti AVR surinkėjo versiją.

6.6 „FlashROM“ prieigos komanda

Komandai su kvietimu į „FlashROM“ baitas perkeliamas (nukopijuojamas) iš pusės „FlashROM“ atminties langelio į bendrąjį registrą R0. Komanda aprašyta 4 lentelėje. 2.7. Kompiuterio komandos kodas yra žodžio formatu. Komanda vykdoma trimis ciklais.

Prieš vykdant komandą, adresas, atitinkantis atminties vietą „FlashROM“, kurioje saugoma konstanta, turi būti padaugintas iš 2 ir įrašytas į Z registrų porą (Nr. 30 USD, 31 USD).

Padauginus iš 2 (kodą perkelkite į kairę vienu skaitmeniu), skaitmenis 0 yra žemesne ZL registro tvarka (30 USD). Jei žemesnioji eilė lygi nuliui, baitas parenkamas iš apatinės „FlashROM“ langelio pusės. Norėdami pasirinkti baitą iš viršutinės langelio pusės, skaičius, kurio kodas yra Z registrų poroje, turi būti padidintas 1, naudojant komandos numerį 33 su mnemoniniu kodu ADIWR30, 1 arba ADIWZL, 1.

Programuojant mikrovaldiklį, konstantos rašomos „FlashROM“.

6.7 „Bit“ operacijų komandos

Operacijos su bitais komandos aprašytos 4 lentelėje. 2,8 ir 2,9. Visų komandų mašinų kodai yra žodžio forma. Komandos Nr. 65 ir 66 yra vykdomos per 2 priemones, likusios komandos - po 1.

Lentelėje. 2.8 naudojamas šis naujas pavadinimas:

▪ PrP.b - I / O registro b bitas (b \u003d 0 - 7), kurio numeris P (P \u003d 00 - 1 F (!)), Šiek tiek PrP.b bitų.

Komandais Nr. 63 ir 64 bitai perduodami (nukopijuojami) tarp nurodyto bendrojo registro bito ir SREG registro bito.

Komandomis Nr. 65 ir 66 nurodytas įvesties ir išvesties registro bitas nustatomas į reikiamą būseną (atitinkamai 0 arba 1), o komandomis Nr. 67 ir 68 nustatomas nurodytas SREG registro bitas.

Rašant komandų Nr. 65 ir 66 mnemoninį kodą, vietoj registro numerio (P) gali būti nurodytas jo simbolinis pavadinimas, o vietoj bitų skaičiaus (b) gali būti nurodytas simbolinis kategorijos pavadinimas. AVR mikrovaldiklių šeimoje daugelio I / O registrų bitai turi įprastus pavadinimus. Šie pavadinimai pateikiami tekste svarstant įrenginius, kuriuose šie bitai naudojami.

Kai kurių tipų mikrovaldikliuose to paties registro to paties pavadinimo bitai turi skirtingus skaičius. Naudojant standartinius įvesties-išvesties registrų pavadinimus standartiniuose juose esančių bitų pavadinimuose, atitinkamo tipo mikrovaldikliui reikia naudoti AVR versiją „Assembler“.

Priskiriant įprastą kategorijos pavadinimą, buvo suprantama, kad ši kategorija priklauso konkrečiam I / O registrui, tačiau registro pavadinimas / numeris ir kategorijos pavadinimas turi būti nurodyti komandų Nr. 65 ir 66 mnemoniniame kode.

Reikalinga bitų reikšmė (0 arba 1) įvesties ir išvesties registrų bituose su skaičiais nuo 20 USD iki 3F yra nustatoma naudojant registrų operacijas atitinkamai su mnemoniniais kodais CBR (Nr. 29) ir SBR (Nr. 31).

Lentelėje. 10 pav. Parodyti komandų, pagal kuriuos SREG registro bitai nustatomi į tam tikrą būseną (0 arba 1), mnemoniniai kodai nenurodant komandos mnemonikos bitų skaičiaus.

6.8 Programos valdymo komandos

Programos valdymo komandų grupę sudaro komandos besąlygiškiems ir sąlyginiams perėjimams, perėjimui į energijos taupymo režimą, budėjimo laikmačio paleidimui iš naujo ir komandai „neveikiant“.

Lentelėje. 11 aprašytos besąlyginio perėjimo (Nr. 85 ir 86), besąlyginio perėjimo su grįžimu (Nr. 87 ir 88), grįžimo iš paprogramės (Nr. 89) ir grįžimo iš pertraukimo programos (Nr. 90) komandos. Lentelėje naudojami šie nauji pavadinimai:

▪ PC - komandų skaitiklis;

▪ (PC) - numerio kodas komandų skaitiklyje;

▪ k - skaičiaus padidėjimas komandos skaitiklyje.

Rašant programą surinkimo kalba, komandų Nr. 85 ir 87 mnemoniniuose koduose vietoj k padidinimo etiketė (simbolinis adresas) rašoma prieš komandos mnemoninį kodą, į kurį turite tęsti. Padidėjimas apskaičiuojamas ir sudedamas į komandos mašininį kodą surinkimo metu.

Mašinos kodo komandos aprašytos lentelėje. 11 turi žodžio formatą. Besąlyginės šuolio komandos (Nr. 85 ir 86) vykdomos dviem ciklais, besąlyginės šuolio komandos ir grįžimas (Nr. 87 ir 88) vykdomos 3 ciklais, grįžimo komandos (Nr. 89 ir 90) vykdomos 4 ciklais.

Sąlyginės šakos komandų grupė yra padalinta į dvi grupes. Pirmojo pogrupio komandose kaip sąlyga naudojama lygybė nuliui arba lygybė vieno iš SREG registre esančių bitų vienybei. Pirmojo pogrupio komandų sąlygos ir mnemoniniai kodai pateikti lentelėje. 12. Jei įvykdoma sąlyga, pereinama prie adreso, kuris suformuojamas naudojant padidėjimą k, nurodytą komandos kode ((PC) + 1 + k → PC; -64 ≤k≤ 63).

Jei šios sąlygos nesilaikoma, programa eina į kitą komandos komandą ((PC) + 1 → PC).

Rašant programą surinkimo kalba, komandoje mnemonic vietoj k padidinimo, prieš komandą mnemonic rašoma etiketė (simbolinis adresas), kuriai vykdyti reikia tęsti, jei tenkinamos sąlygos.

Pirmojo pogrupio komandų mašinų kodai yra „žodžio“ formato. Kai įvykdoma sąlyga, komanda vykdoma dviem ciklais, įvykdžius sąlygą - per 1 ciklą.

Jei sąlygos neįvykdoma, atliekamas perėjimas prie kitos komandos programoje ((PC) + 1 → PC). Jei sąlyga įvykdyta, pereinama prie komandos vykdymo sekant kitą ((PC) + 1 + 1/2 → PC). Skaičiaus prieaugis komandų skaitiklyje (1 arba 2) nustatomas pagal kitos komandos mašinų kodo formatą (atitinkamai 1 žodis arba 2 žodžiai).

Antrojo pogrupio sąlyginių šakų instrukcijų mašinų kodai turi žodžio formatą. Komandos vykdomos vienu laikrodžio ciklu, jei nėra įvykdyta sąlyga, per 2 laikrodžio ciklus, jei sąlyga įvykdyta, o kita komanda (K1) turi žodžio formatą, arba per 3 laikrodžio ciklus, jei sąlyga netenkinama, o kita komanda (K1) turi „2 žodžių“ formatą. “.

Nuorodos

1. Belovas A.V. Savamokslis prietaisų kūrėjas AVR mikrovaldikliuose. - Sankt Peterburgas, „Mokslas ir technika“, 2010 m

2. http://www.atmel.ru/

3. „ATtiny 2313“ duomenų lapas.

4. Grebnevas V.V. AVR firmų „Atmel“ šeimos mikrovaldikliai. –M. „IP RadioSoft 2002“

„Atmel“ yra gerai žinomas pasaulio ir Rusijos rinkose kaip plataus asortimento mikroschemų, turinčių lustinę atmintį, gamintojas. Pavyzdžiui, ATF16V8 / 20V8 / 22V10 ir AFT15xx serijos programuojamuose loginiuose lustuose yra EEPROM konfigūracijos ROM, AT89C mikrovaldikliuose yra Flash programos ROM, o AVR mikrovaldikliai naudoja tiek Flash, tiek EEPROM viename luste. „Atmel“ mikroschemų sąraše, pavyzdžiui, yra dviejų bankų „Flash“ atmintis, palaikanti paketinį režimą, taip pat „sluoksninės“ mikroschemos, kuriose kristalai, lygiagretus ROM, nuoseklusis ROM ir RAM yra viename korpuse, bet ant skirtingų „sluoksnių“. Šis straipsnis, kuris nepretenduoja į neišsamumą, yra skirtas „Atmel ROM“ lustoms „gryna forma“.

„Atmel“ yra novatoriškas gamybos nestabilios atminties lustus srityje: jis pirmasis 1989 m. Išleido „Flash“ atminties lustus, kurių programavimo įtampa yra 5 V; pirmasis pasaulyje pradėjo gaminti „Flash“ atmintį 3,3, 2,7 ir 2,5 V įtampai; 1997 m. „Atmel“ korporacija pirmoji pasiūlė „flash“ atmintį su nuoseklia sąsaja. Ir sąrašas tęsiasi ...

Dabartinės „Atmel“ nestabilios atminties mikroschemų talpa svyruoja nuo 1 Kbps iki 256 Mbps, o netrukus bus pradėta gaminti 1 Gbit grandines. Produktų asortimentą sudaro mikroschemos su 8 ir 16 bitų lygiagrečia sąsaja, taip pat mikroschemos su dviejų ir trijų laidų nuosekliąja sąsaja.

Paraleliniai lustai

Anksčiau nei kiti buvo išleisti AT27 serijos lustai su 8 bitų sąsaja, kurie iš tikrųjų buvo ROM lustų analogai su ultravioletiniu trynimu, tačiau „Atmel“ kristalai buvo supakuoti plastikinėse dėžutėse, o tai žymiai sumažino lustų kainą. „Pigumo“ kaina yra neįmanoma perprogramuoti. Kai prireikė skubiai atnaujinti atminties lusto turinį sistemoje, pavyzdžiui, atnaujinti versiją, „Atmel“ pasiūlė tris lygiagrečių ROM lustų serijas su elektriniu trynimu.

AT28 serija, pagrįsta EEPROM technologija, turi funkciją savarankiškai perrašyti kiekvieną baitą, o tai lemia lusto srities padidėjimą ir atitinkamai lusto kainą. Serijose AT29 ir AT49, pastatytose remiantis „Falsh“ technologija, įgyvendinamas skirtingas požiūris - čia galima perrašyti blokuose, vadinamuose sektoriais. AT29 atminties lustų sektoriaus dydis yra mažesnis nei kitų gamintojų lustų, o tai padidina naudojimo lankstumą. AT49 serijoje yra keli sektoriai didelis dydis ir dėl to jo kristalų plotas yra mažesnis, o vieneto kaina mažiausia. Kitaip nei AT28 serijos mikroschemose, kai trinti reikia 12 V, modernesniems AT29 ir AT49 nereikia papildomo įtampos šaltinio trinti ir perprogramuoti. Patogus technologinis sprendimas yra organizuoti įkrovos bloką atminties masyve su atskiromis komandomis, siekiant apsaugoti jį nuo ištrynimo. Įkėlimo programa paprastai yra šioje atminties srityje, kurioje taip pat gali būti įrankis, atliekantis pagrindinio ROM masyvo programavimo funkciją, pavyzdžiui, iš nuosekliojo prievado. Ši sistemos konstrukcija leidžia modifikuoti „Flash-ROM“ turinį nenaudojant išorinio programuotojo. Antras pranašumas yra tas, kad TSSOP atvejais galite naudoti mažo dydžio mikroschemas ir atsisakyti plokščių, skirtų ROM.

Aukščiau pateiktų šeimų mikroschemos yra prieinamos trims maitinimo įtampoms: standartinėms penkių voltų grandinėms, veikiančioms 3,3 V (pažymėtos raidėmis LV) ir 2,7 V (pažymėtomis raidėmis BV) maitinimo grandinėms:.

Pagrindiniai tipiškų ROM lustų AT49BV serijos parametrai pateikti lentelėje. 1.

1 lentelė

* N arba T - įkrovos blokas apatiniu arba viršutiniu adresais.

Lustai su lygiagrečia sąsaja daugiausia naudojami mikroprocesoriaus programai, kuri vykdoma tiesiai iš ROM, saugoti, jei mikroprocesoriaus greitis yra santykinai mažas, arba prieš pradedant vykdymą yra nukopijuojamas į RAM, kas būdinga šiuolaikiniams mikroprocesoriams. „Lygiagrečiai“ ROM lustai taip pat gali būti naudojami duomenims saugoti. Tam buvo naudojami net vieno lusto arba ultravioletiniu būdu sunaikinami mikroschemos, o atsiradus pirmiesiems „Flash ROM“ įrenginiams, duomenų rinkimo sistemų kūrėjams buvo suteikta galimybė.

Tačiau mikroschemos su lygiagrečia sąsaja turi trūkumų dėl pačios architektūros. Norint atlikti rašymo ir skaitymo operacijas, reikia dirbti su trimis magistralėmis: adresu, duomenimis ir valdymu. Jei mikrovaldiklis naudoja multipleksuotą adresų-duomenų magistralę, plokštėje turi būti įdiegti papildomi fiksatorių registrai, kad būtų išsaugotas adresas, kuris bus naudojamas prieigai prie atminties kito laikrodžio ciklo metu. Bet net jei mikrovaldiklis turi atskiras adresų ir duomenų magistracijas, būtina „išskaidyti“ visas spausdintinės plokštės grandines. 1 MB talpos lustui reikia 20 laidininkų pagal adresą ir 8 laidininkų duomenims, jei naudojama mikroschema su baito sąsaja, plius valdymo signalai, kurie kartais užima didelę dalį spausdintinės plokštės, ypač jei sukurtam įrenginiui keliami didesni reikalavimai, atsižvelgiant į bendruosius matmenis.

Kitas trūkumas yra padidėjęs prietaiso energijos suvartojimas. Yra žinoma, kad nemaža dalis lusto sunaudojamos elektros energijos sunaudojama jo išvesties etapuose, o tai turėtų užtikrinti gerą signalo frontą dirbant prie pakankamai didelės talpos išorinės magistralės. Pagrindinis problemos sprendimas yra atsisakyti lygiagrečios magistralės ir pereiti prie serijinių duomenų mainų.

Serialo žetonai

Atsižvelgiant į bendrą norą sumažinti energijos suvartojimą ir elektroninių prietaisų miniatiūrizavimą, nuosekliųjų atminties lustų naudojimas tapo skubus. „Atmel“ serijinių ROM lustų populiarumas iškalbingas tuo, kad bendrovė pagamino daugiau nei milijardą tokių lustų. „Atmel“ gamina universaliąsias atminties mikroschemas su I2C, SPI ir Microware sąsajomis, taip pat specializuotas AT17 serijos konfigūracijos atminties mikroschemas, skirtas FPGA tipo programuojamoms loginėms mikroschemoms įkelti. Šias mikroschemas sistemoje galima pakartotinai perprogramuoti. Pastebėtina, kad AT17 lustai gali būti naudojami ne tik kraunant pačių „Atmel“ FPGA - AT6000 ir AT40K, bet ir norint krauti „Xilinx“ ir „Altera“ pagamintus FPGA. Pastariesiems atsisiųsti skirta AT17A šeima, kuri, remiantis išvadomis, suderinama su „Altera“ EPC mikroschemomis. Reikėtų pažymėti, kad pradėjus masinę naujų didelės talpos konfigūracijos atminties lustų gamybą, „Atmel“ lenkia kitas firmas. Visų pirma, ji buvo pirmoji pasaulyje, gaminanti žemos įtampos lustą, kurio talpa 2 Mbit, 8 kontaktų plokštumoje.

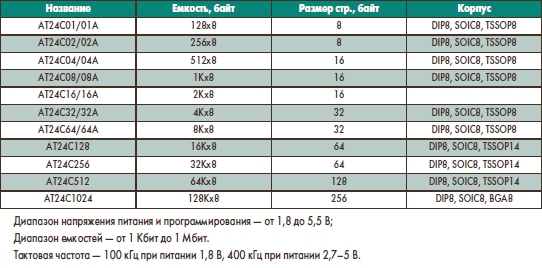

Visuotinės nuosekliosios ROM lustai su pakankamu sąlygiškumo laipsniu gali būti suskirstyti į „lėtą“ ir „greitą“. Pirmai kategorijai priklauso AT24 serijos lustai su I 2 C sąsaja. Ši „Philips“ sukurta dviejų laidų sąsaja yra labai patogi keistis mažais duomenų fragmentais, kurių dažnis neviršija šimtų kilohercų. Tipiškas pavyzdys yra buitinis televizorius arba kompiuterio monitorius su atminties nustatymais. AT24 serijos lustai pasižymi dideliu perrašymo ciklų skaičiumi - iki milijono kartų. Patogi kokybė yra galimybė padidinti autobuso mikroschemų skaičių iki 4–8 vienetų, nepridedant papildomų valdymo signalų. Tam reikia dviejų ar trijų adresų kaiščių, esančių ant atitinkamų laidų. AT24 lustų nomenklatūra yra gana plati. Mikroschemos išsiskiria galimybe apsaugoti programinę įrangą nuo visos atminties masyvo ar jo dalies (pusės ar ketvirtadalio visos mikroschemų talpos) užrašymo.

Pagrindiniai tipiškų AT24 serijos mikroschemų parametrai pateikti lentelėje. 2.

2 lentelė

Programose, kurioms reikalingas padidintas duomenų mainų greitis, atminties mikroschemų naudojimas su „Motorola“ sukurta SPI sąsaja yra optimalus. „Atmel“ SPI mikroschemų veikimo greitis yra nuo 2 iki 50 MHz. Reikėtų paaiškinti, kad yra dvi mikroschemų veikimo greičio savybės: minėtasis, kuris parodo užsienio valiutos keitimo greitį ir ROM lusto buferį, ir buferio turinio fizinio kopijavimo į atminties masyvą greitis.

Apsikeitimui su SPI ROM naudojami keturi signalai: laikrodžio impulsai, įvesties duomenys, išvesties duomenys ir signalo „lusto pasirinkimas“. Ši architektūra gali žymiai sutaupyti vietos spausdintinėje plokštėje, ypač kai įrenginyje naudojamos kelios mikroschemos.

„Atmel“ gamina dvi ROM atmintinių grupes su SPI sąsaja: AT25 serija, sukurta naudojant EEPROM technologiją, ir AT45 serija, sukurta naudojant Flash technologiją. „AT25“ serijoje, kurios pagrindas yra „Flash“ technologija, yra atstovai - tai AT25F512 / 1024 lustai. AT25 serijos blykstės IC turi didesnį keitimo kursą, tačiau mažiau rašymo ciklų (10 000 kartų).

Pagrindiniai AT25 serijos lustų parametrai pateikti 3 lentelėje.

3 lentelė

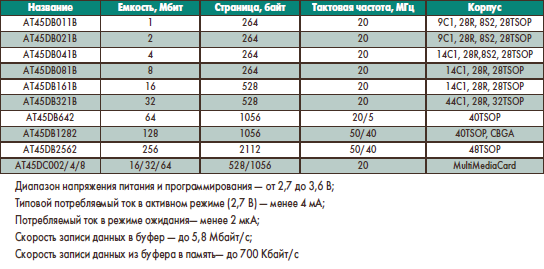

Įdomiausia istorija yra lustų šeimos AT45 plėtra, sukurta remiantis „Atmel“ patentuota „DataFlash ®“ architektūra. Ši šeima savo vystymuisi jau išgyveno kelias kartas. Pirmos kartos AT45D011 - AT45D161 mikroschemos buvo pagamintos naudojant 0,35 mikronų technologiją ir jų maitinimo įtampa buvo 5 V (šios mikroschemos šiuo metu nebegaminamos). Trys skaičiai lusto pavadinime reiškia taip: pirmieji du yra lusto talpa megabaitais, trečiasis - įvesties / išvesties prievadų skaičius. Krištolo matmenys buvo gana dideli, todėl jie buvo supakuoti į SOIC28 dėžutes, o dauguma išvadų liko nesusijusios. Taigi toje pačioje vietoje buvo galima įdiegti bet kokio galingumo lustą. Netrukus „Atmel“ įsisavino žemos įtampos maitinimo grandinių AT45DB011 - AT45DB321 gamybą. Naujausias lustas buvo išleistas TSSOP32 pakete. Perėjus prie 0,25 mikrono technologijos, kristalų plotas buvo žymiai sumažintas, o dabar 1, 2 ir 4 Mbit mikroschemos gaminamos net SOIC8 pakuotėse.

Nors perėjus prie 0,25 mikrono technologijos, SPI duomenų mainų sparta padidėjo iki 20 MHz, to nepakako didelės talpos mikroschemoms. Norėdami pašalinti silpnąją vietą, 64 Mbit ir didesnės talpos mikroschemose buvo įrengta papildoma 8 bitų sąsaja. Taigi AT45DB642 mikroschema gali būti pasiekiama vienu metu dviejuose prievaduose, o nuoseklios prieigos taško dažnis yra 20 MHz, lygiagrečiai - 5 MHz.

Naujos „DataFlash ® AT45DB1282“ ir „AT45DB2562“ mikroschemos, kurių atitinkamai 128 ir 256 Mb, yra pagamintos naudojant 0,18 mikrono technologiją. Ši technologija leido padidinti keitimo greitį iki 50 MHz per SPI sąsają ir iki 40 MHz naudojant baitų sąsają. Jei SOIC atvejai buvo laikomi tipiškais ankstesnių kartų AT45 mikroschemų atvejais, tada TSOP atvejai tapo standartiniais naujiems didelės talpos mikroschemoms.

Lustai tiekiami dėžutėse. skirtingų dydžių (TSOP32, TSOP40 ir TSOP48), tačiau jie yra suderinami montuojant ant spausdintinės plokštės. Pažvelgę \u200b\u200bį aukščiau nurodytus mikroschemų taškus, galite pamatyti, kad TSOP40 atveju aštuoni kraštiniai laidai (keturi iš kiekvieno krašto) nenaudojami. Panaši situacija yra ir TSOP48 atveju, tik čia yra šešiolika laisvų kaiščių. Taigi, jei TSOP48 dėklas yra laidinis ant spausdintinės plokštės, šioje plokštėje galite įdiegti 64, 128 arba 256 Mbit lustą.

Šiuo metu prieinamos AT45 lustų linijos talpa svyruoja nuo 1 Mbps iki 256 Mbps. Ruošiantis pramoninei gamybai naudojant 0,13 mikronų technologiją, yra 512 ir 1024 Mbps spartos mikroschemos. Be tikrųjų atminties lustų su SPI sąsaja, „Atmel“ taip pat siūlo MMC (MultiMediaCard) formato modulius, kurių talpa yra 2, 4 ir 8 MB, su 7 kontaktų jungtimi ir atitinkama sąsaja.

Naudodamiesi SPI sąsaja, kūrėjas gali šiek tiek pastangų pereiti prie didesnės talpos mikroschemų naudojimo. Paprastai tam pakanka pakeisti dvi konstantas darbui su SPI ROM - puslapio dydį ir šios mikroschemos puslapių skaičių.

Kitaip nei kitų gamintojų didelės talpos blykstės atminties IC, „Atmel“ mikroschemose atminties masyve nėra trūkumų turinčių bitų, todėl nereikia duomenų įrašymo kokybės kontrolės procedūros. AT45 mikroschemose yra penkių voltų tolerantiški įėjimai ir išėjimai, kurie leidžia juos tiesiogiai prijungti prie penkių voltų mikrovaldiklių.

Pagrindiniai AT45 serijos lustų parametrai pateikti lentelėje. 4.

4 lentelė

Straipsnio pabaigoje pateikiamas atminties funkcijos AT45 pavyzdys. AVR mikrovaldiklis buvo naudojamas kaip valdymo procesorius. Programa parašyta C forma „ImageCraft Company“ sudarytojui. 30 dienų demonstracinę šio kompiliatoriaus versiją galite rasti „Atmel“ svetainėje http://atmel.argussoft.ru/soft.htm. Failo dydis yra 3,9 MB. „At45.h“ papildinio failas yra http://atmel.argussoft.ru/as-mega.htm.

Vienas didžiausių puslaidininkių elektroninių grandynų gamintojų yra . Mikrovaldiklius, nestabilius atminties modulius, sudėtingas logines integruotas grandines ir puslaidininkių komponentus, skirtus apdoroti „Atmel“ mišrius signalus, galima rasti statant daugybę elektronikos ir kitų modernių technologijų.„Atmel“ gaminių ženklinimo ypatybės

Visam įmonės gaminamų gaminių asortimentui buvo sukurtas vieningas ženklinimo etiketėmis standartas, kuriame atsižvelgiama į tam tikros grupės mikroschemų techninių parametrų įvairovę.Visi „Atmel“ gaminami lustai yra pažymėti AT AT XXXXX - X X X X (X simbolis žymi raidinius ir skaitmeninius simbolius). Jei atsižvelgsime į juos tvarkingai, gausime:

- AT - visų įmonės pagamintų mikroschemų žymėjimas;

- XXXXX - nurodykite grupę, tipą, gamybos technologiją;

- X - rodo prietaiso greitį;

- X yra grandinės korpuso tipas;

- X yra darbinių temperatūrų diapazonas;

- X - vykdymo galimybės.

- grupė, kuriai priklauso grandinė (įvairių tipų atmintis, loginės grandinės, mikrovaldikliai);

- atminties tipai (mikroprocesoriai, tik skaitoma ir nuosekli atmintis, programuojami ir perprogramuojami);

- grandinei gaminti naudojama technologija;

Apsvarstykite šį žymėjimo pavyzdį : ATMEGA165PV-8AU:

- po pirmųjų dviejų raidžių, nurodančių gamintoją, šeimos, kuriai priklauso šis mikrovaldiklis, žymėjimas yra MEGA;

- skaičiai 16 atitinka į mikroschemą integruotos Flash atminties kiekį, išreikštą kb;

- skaičius 5 nurodo valdiklio versiją;

- raidė P yra „picoPower“ gamybos technologija, užtikrinanti ekonomišką srovės suvartojimą režimu iki 100 nA, esant „Power down“ režimui;

- V - atitinka darbinės įtampos diapazoną nuo 1,8 iki 5,5 volto;

- skaičius 8 rodo maksimalų lusto veikimo dažnį;

- raidė A atitinka TQFP tipo korpusą;

- U žymi kristalo darbinės temperatūros diapazoną nuo -40 ° C iki +85 ° C ir poreikį naudoti lydmetalį be švino dirbant su grandine.

„Nuoroda“ - informacija apie įvairius elektroniniai komponentai: tranzistoriai, mikroschemos, transformatoriai, kondensatoriai, Šviesos diodai tt Šioje informacijoje yra viskas, kas būtina komponentų atrankai ir inžineriniams skaičiavimams, parametrams, taip pat gaubtų išdėstymas, tipinės instaliacijos schemos ir naudojimo rekomendacijos. radijo elementai.

„Atmel® DataFlash®“ atminties lustai idealiai tinka naudoti įvairiose techninėse programose, nepriklausomai nuo to, kokius duomenis norite saugoti. Kadangi „DataFlash“ veikia kaip didelės talpos nuosekli EEPROM (elektriškai valoma programuojama skaitymo tik atmintis), ji gali būti naudojama daugelyje techninių programų, o tai gali žymiai sumažinti kainą gatavas produktas. Šiame straipsnyje bus aptariami AT45DBxx1D serijos lustai.

Bendras aprašymas

AT45DBxx1D serijos lustai yra idealiai tinkami naudoti įvairiose techninėse programose, kai reikia saugoti suskaitmenintus duomenis, kalbą, atvaizdą ar tiesiogiai programos kodą. Visi AT45DBxx1D serijos atminties lustai palaiko „RapidS ™“ nuosekliąją sąsają, kuri reikalinga programoms, kurioms reikalingas įrenginio veikimas dideliu duomenų perdavimo greičiu. „RapidS ™“ yra suderinamas su SPI (Serial Peripheral Interface), skirtas laikrodžio greičiui iki 66 MHz. Kiekvieno iš šios serijos atstovų visa atmintis yra sutvarkyta kaip tam tikro tūrio puslapių rinkinys. Puslapių skaičius ir jų dydis nustatomi atsižvelgiant į konkretų lusto modelį. Be pagrindinės atminties, šios serijos mikroschemose yra vienas ar du papildomi statinės atminties buferiai (žr. 1 lentelę), kurie leidžia priimti duomenis perprogramuojant („mirksint“) pagrindinę atmintį, taip pat įrašyti nenutrūkstamą duomenų srautą. Be to, visos perprogramavimo / trynimo operacijos yra sinchronizuotos. EEPROM emuliaciją galima lengvai atlikti naudojant autonominę trijų pakopų skaitymo / modifikavimo / rašymo procedūrą. Skirtingai nuo įprastos „Flash“ atminties, kuri suteikia galimybę atsitiktine prieiga naudotis bendrais adresų magistralėmis ir lygiagrečia sąsaja, „DataFlash®“ lustai nuosekliajai duomenų prieigai naudoja „RapidS ™“ sąsają. Tokia paprasta duomenų prieigos schema žymiai sumažina aktyviųjų mikroschemų išėjimų skaičių, o tai leidžia sumažinti prietaiso, kuriame jis naudojamas, masines savybes, taip pat padidinti jo patikimumą ir sumažinti perjungimo triukšmą. Taigi, AT45DBxx1D serijos lustai yra optimizuoti naudoti įvairiose komercinėse ir pramoninėse reikmėse, kur reikalingas kompaktiškumas, žemos įtampos ir mažos energijos sąnaudos. Norėdami supaprastinti mirksėjimo procedūrą, AT45DBxx1D serijos mikroschemai, priklausomai nuo tipo, reikalingas vienpolis energijos šaltinis, kurio įtampa yra 2,5 ... 3,6 V (arba 2,7 ... 3,6 V). Kiekvienas lustas iš nagrinėjamos serijos yra valdomas per CS lusto pasirinkimo kaištį (Chip Select), o duomenys pasiekiami per 3 laidų sąsają, įskaitant SI nuoseklųjį įvestį (nuoseklųjį įvestį), nuoseklųjį išėjimą (nuoseklųjį išėjimą) ir laikrodžio sinchronizavimą (nuoseklųjį laikrodį). ) Lentelėje pateikiami pagrindiniai skiriamieji AT45DBxx1D serijos lustų bruožai ir charakteristikos. 1. Išvadų ir išvaizda serijos AT45DBxx1D mikro grandinės įvairiais atvejais parodytos fig. 1.

Fig. 1. AT45DBxx1D serijos lustų išdėstymas ir išvaizda įvairiose pakuotėse: a - MLF8, b - SOIC8, c - TSOP28

1 lentelė. Pagrindinės AT45DBxx1D serijos lustų savybės ir specifikacijos

|

Vardas |

Talpatruputį |

Upitas B |

Sąsaja |

RAM buferis, baitas |

Skaičiusišvados |

Kūno tipas |

Dydispuslapiųbaitas |

Skaičiuspuslapių |

Dydisblokuotikbyte |

Dydissektoriaikbyte |

|

MLF8, TSOP28, SOIC8 |

||||||||||

Pagrindinės AT45DBxx1D serijos mikroschemų savybės

Mes išvardijame pagrindines „AT45DBxx1D“ serijos „Flash“ atminties mikroschemų savybes:

Maitinimas iš vienpolio šaltinio, kurio įtampa yra 2,5 ... 3,6 V arba 2,7 ... 3,6 V;

„RapidS ™“ sąsaja (laikrodžio dažnis iki 66 MHz) suderinama su SPI;

Vartotojo konfigūruojamas atminties puslapio dydis (žr. 1 lentelę);

Intelektuali programavimo funkcija;

Lanksčios duomenų ištrynimo parinktys:

- galimybė ištrinti puslapius / blokus / sektorius (žr. 1 lentelę);

- visiškas trynimas;

Papildomos buferinės statinės RAM;

Galimybė nuskaityti nenutrūkstamą duomenų srautą (idealiai tinkama programoms, naudojančioms šešėlinę RAM);

Mažos energijos sąnaudos:

- 7 mA - aktyviame režime;

- 25 μA - budėjimo režime;

- 5 μA (9 μA lustui, pavyzdžiui, AT45DB161D) - neprisijungęs;

Aparatinės ir programinės įrangos apsaugos funkcijos;

Sektorių blokavimas siekiant apsaugoti programos kodą ar saugomus duomenis;

Privati \u200b\u200bprieiga prie duomenų naudojant slaptą 128 baitų registrą:

- 64 baitų vartotojo programuojama erdvė